# How Computers Work

# Processor and Main Memory

# Roger Young

© Copyright 2001, Roger Stephen Young All rights reserved.

No part of this book may be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the author.

#### **FREE**

An identical Internet version of this book is available for free (for personal use and, possibly, for a limited time) at

#### http://howcomputers.com

and/or at

http://www.geocities.com/thinkorrr/howcomputerswork/p1.html

## I'm at thinkorrr@yahoo.com

and I'll (possibly for a limited time) send you a free Microsoft Word 2000 .doc file version (for personal use) as an attachment to an email if you email me and want one.

March 20, 2002

#### Introduction

Computers are the most complex machines that have ever been created. Very few people really know how they work. This book will tell you how they work and no technical knowledge is required. It explains the operation of a simple, but fully functional, computer in *complete* detail. The simple computer described consists mainly of a processor and main memory. Relays, which are explained, are used in the circuitry instead of transistors for simplicity. This book does not cover peripherals like modems, mice, disk drives, or monitors.

Did you ever wonder what a bit, a pixel, a latch, a word (of memory), a data bus, an address bus, a memory, a register, a processor, a timing diagram, a clock (of a processor), an instruction, or machine code is? Though most explanations of how computers work are a lot of analogies or require a background in electrical engineering, this book will tell you precisely what each of them is and how each of them works without requiring any previous knowledge of computers or electronics. However, this book starts out very easy and gets harder as it goes along. You must read the book starting at the first page and not skip around because later topics depend on understanding earlier topics. How far you can get may depend on your background. A junior high school science background should be enough. There is no mathematics required other than simple addition and multiplication. This is a short book, but it must be studied carefully. This means that you will have to read some parts more than once to understand them. Get as far as you can. You will be much more knowledgeable about how computers work when you are done than when you started, even if you are not able to get through the whole text. This is a technical book though it is aimed at a non-technical audience. Though this book takes considerable effort to understand, it is very easy for what it explains. After you have studied this book, if you go back and read it, it will seem simple. Good Luck!

## **CONTENTS**

| BASICS        | 7   |

|---------------|-----|

| MEMORY        | 43  |

| INSTRUCTIONS  | 81  |

| PROCESSOR     | 101 |

| PROGRAMMING   | 132 |

| MISCELLANEOUS | 156 |

# **BASICS**

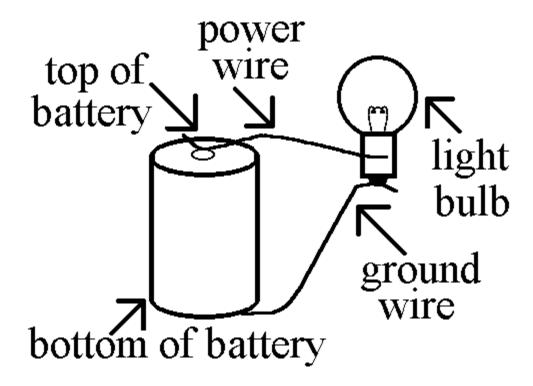

#### **Simple Circuit**

The picture above shows a 'battery' connected to a 'light bulb' by a 'power wire' and a 'ground wire.' A power wire is a wire connected directly to the top of the battery. A ground wire is a wire connected directly to the bottom of the battery. Any electrical machine is called a circuit.

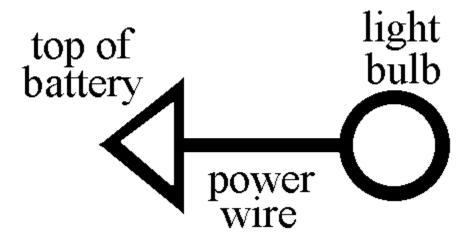

#### Simple Diagram

The diagram above also shows a 'battery' connected to a 'light bulb' by a 'power wire' and a 'ground wire.' This *diagram* means the same as the picture on page 2. *The ground wire is not shown* because it is assumed that one connection of every light is always connected to the bottom of the battery by a ground wire *in diagrams*. Diagrams are simpler to draw than pictures that mean the same thing.

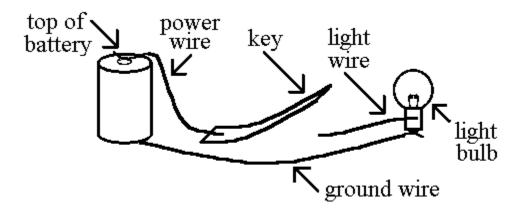

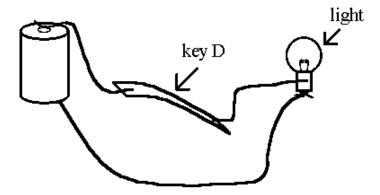

#### **Key Circuit**

The picture above shows the 'top of' a 'battery' connected by a 'power wire' to a 'key' that is connected by a 'light wire' to a 'light bulb.'

A key is a flat piece of springy steel that is bent up so that the key only touches the wire to the key's right when the key is pressed down by someone's finger.

When someone pushes the key down, the right end of the key touches the light wire and electricity flows from the top of the battery, through the power wire, the key, and the light wire, to the light bulb, turning the light bulb on.

When the key is released, the key springs back up. Now the key does *not* touch the light wire and electricity can *not* get from the key to the light wire to the light bulb so that the light bulb goes *off*.

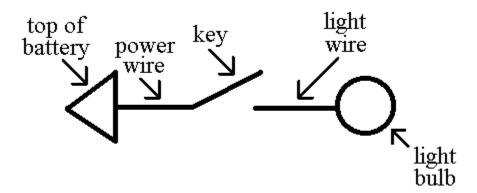

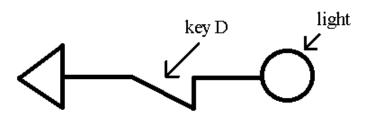

#### **Key Diagram**

The diagram above shows the same circuit as the preceding picture.

Again, there is also a wire from the other connection of the light bulb back to the bottom of the battery, but that wire does not need to be shown because the other connection of every light is connected to the bottom of the battery and you know the ground wire is there without drawing it.

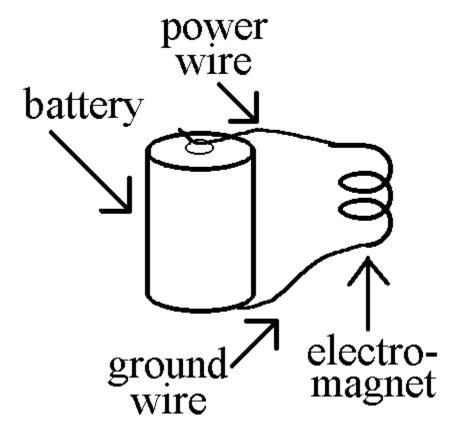

#### **Electromagnet**

The picture above shows the top of a battery connected by a wire to an electromagnet.

An electromagnet is a coil of (plastic coated) wire. An electromagnet becomes magnetic when electricity goes through it, just as a light bulb glows when electricity goes through the light bulb.

The wire that makes up the coil of wire that is the electromagnet has two ends (connections). There is also a 'ground wire' from the other connection of the electromagnet back to the bottom of the battery.

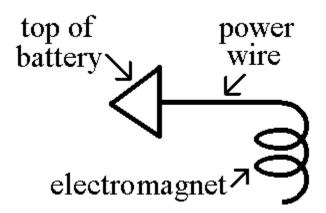

#### **Electromagnet Diagram**

The diagram above shows the same circuit as the preceding picture.

The wire that makes up the coil of wire that is the electromagnet has two ends (connections). There is also a ground wire from the other connection of the electromagnet back to the bottom of the battery, as in the picture, but that wire does *not* need to be shown because the other connection of *every* electromagnet is connected to the bottom of the battery.

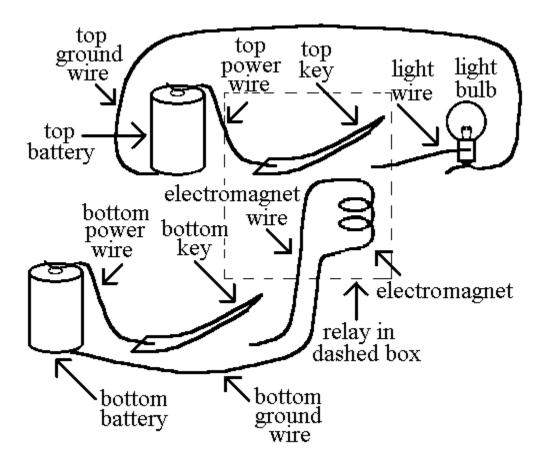

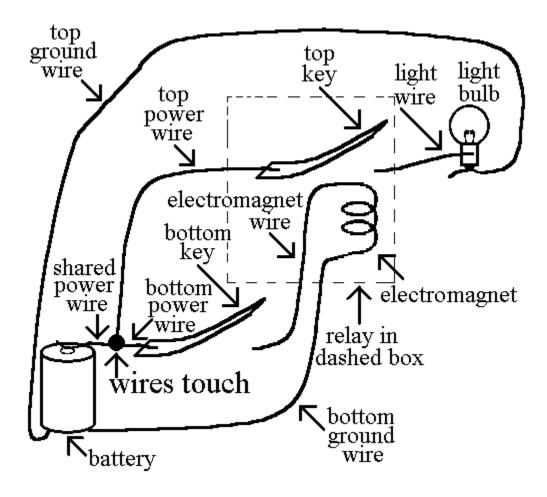

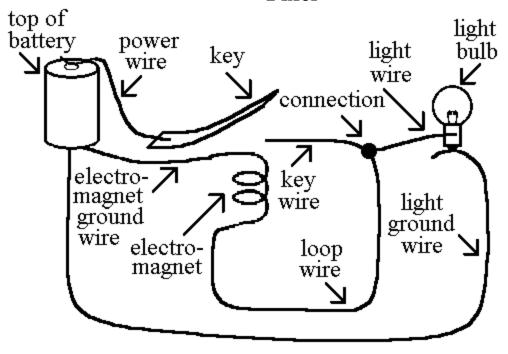

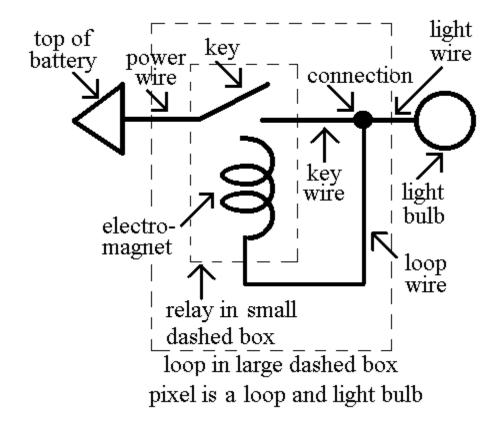

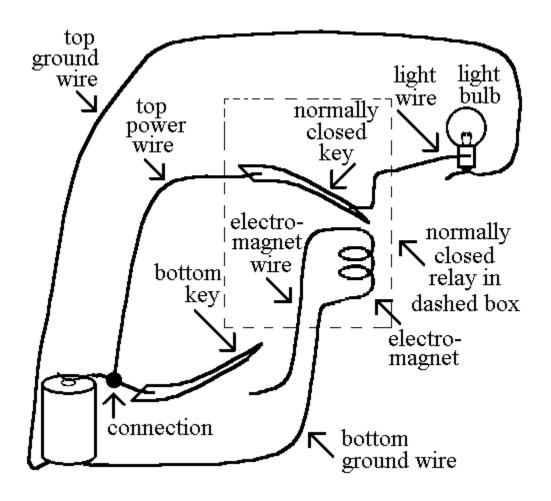

#### Relay

The picture above shows a 'bottom key' that controls an electromagnet.

The electromagnet, in turn, controls the top key. A key and the electromagnet that controls it are, *together*, called a *relay*. The relay is in the dashed box.

When the bottom key is pressed, the electromagnet is powered and the electromagnet becomes magnetic. That makes the electromagnet attract the top key and pull the top key down just like a finger can push a key down. A magnet (or a powered electromagnet) attracts the top key because the top key is made of steel. A magnet (or a powered electromagnet) does not attract the wires because the wires are made of copper.

*Important:* The electromagnet does *not ever* touch the top key. *No* electricity can go from the electromagnet to the wires attached to the top key.

A computer is almost entirely made up of a lot of relays (today, transistors) connected by wires. Just how the relays are connected and just what they do is the main subject of this book. Other concepts, especially programming, will also be explained.

(Today, transistors are used instead of relays for lower cost and greater speed. The design remains practically the same, however. Relays are easier to understand and, so, will be used in this explanation.)

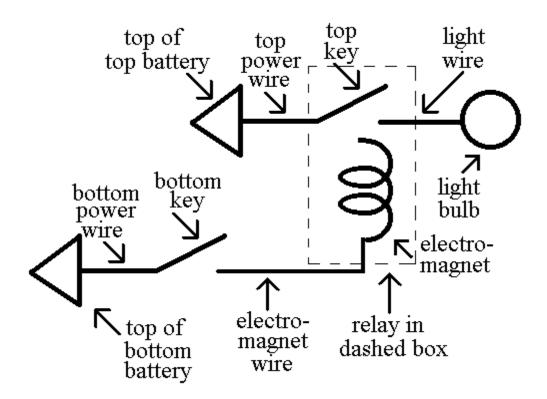

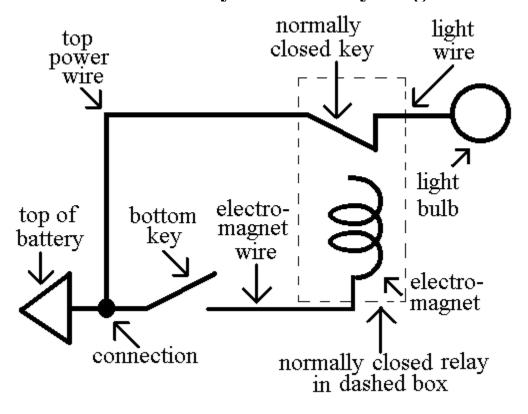

#### **Relay Diagram**

The diagram above shows the same circuit as the previous picture in a different way.

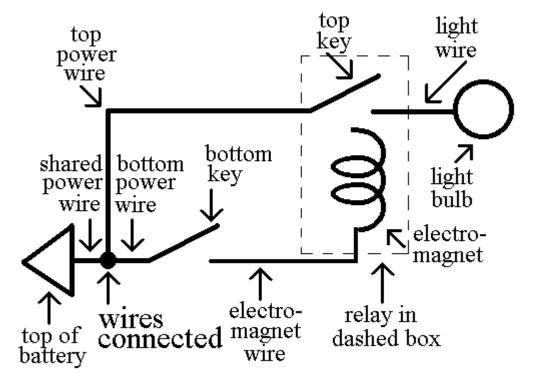

#### **One Battery and Touching Wires**

In this picture, only *one battery* powers all the circuitry in the previous picture. Note the symbol for wires that touch.

#### **One Battery and Connected Wires Diagram**

This diagram shows the same circuit as the previous picture in a different way. Touching wires are connected wires.

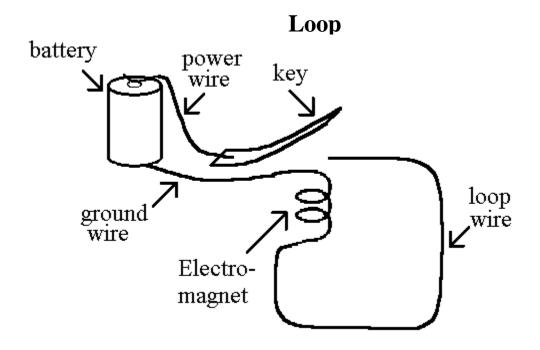

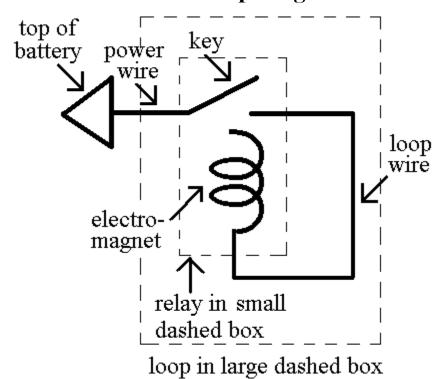

#### **Loop Diagram**

The picture and diagram at left show a relay that controls its *own* electromagnet! The square of wire that takes electricity from the key of the relay to the electromagnet of the same relay is called a 'loop.'

No electricity can get from the top of the battery to the electromagnet because the key is up. However, if someone presses the key, then electricity *can* get to the electromagnet. Then, the *electromagnet* will hold the key down - *even if the person lets go of the key!* So we say that the loop *remembers* that the key was pressed. Remember that the key normally springs up because it is springy and bent upward.

Similarly, if someone then lifts up the key (A person is much stronger than a little electromagnet.), then no electricity will reach the electromagnet and the key will remain up even after the person releases the key. So we say that the loop *remembers* that the key was lifted up.

Most relays in a computer are used to make loops, or connect the loops together.

#### **Pixel**

**Pixel Diagram**

The picture and diagram above show a loop that controls a light bulb. A light bulb that is controlled by a loop is called a 'pixel.'

In a diagram, where a horizontal wire and a vertical wire meet, without crossing, there is a connection of the two wires.

Therefore, when the key is pressed, electricity can flow from the top of the battery, through the key, to both the light and the electromagnet. When the key is down and the light bulb is glowing, one says that the loop has value '1' and the pixel is 'on.' The loop has value '1' even if there is not a light bulb, just so the loop wire has electricity going through it, to the electromagnet, because the key is down.

When the key is *up* and the light bulb is *not* glowing, one says that the loop has value '0' and the pixel is 'off.' The loop has value '0' even if there is not a light bulb - just so the loop wire does *not* have electricity going through it (because the key is up).

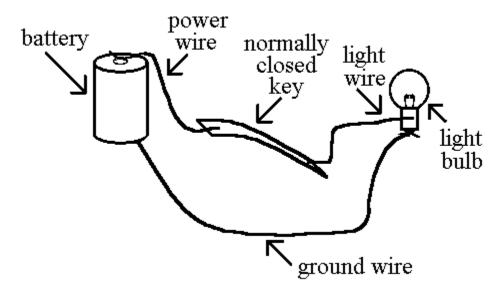

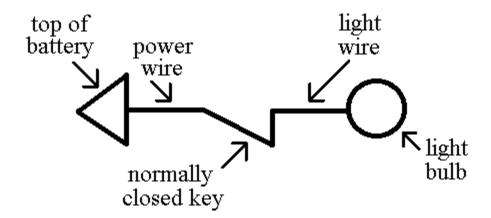

#### **Normally Closed Key**

#### **Normally Closed Key Diagram**

The picture and diagram at left show the top of a battery connected by a wire to a normally closed key, that is connected by another wire to a light bulb.

A diagram of an electrical machine is called a circuit diagram, a diagram, a schematic (pronounced ske-ma'-tic) diagram, or just a schematic.

The normally closed key is different from the keys described previously. The normally closed key is also a springy piece of steel, but is bent so that it normally *is* connected to the right wire. Therefore, the light bulb in the circuit above is normally on. However, if you push *down* on the normally closed key, the light bulb becomes disconnected from the 'power wire' and the light goes out.

A key is called 'closed' when electricity can flow through it from a wire on its left to a wire on its right.

A key is called 'open' when electricity *can't* flow through it from a wire on the left to a wire on the right.

A normally closed key is normally closed, but is open when you push it down. A normally open key is normally open, but is closed when you push it down.

A relay is called closed if its key is closed. A relay is called open if its key is open.

An electromagnet is called 'powered' if the electromagnet is connected to the top of a battery, *even* if that electromagnet is connected to the top of the battery through a series of *closed* keys. In fact, any piece of wire is called 'powered' if that piece of wire is connected to the top of a battery, *even* if that piece of wire is connected to the top of the battery through a series of *closed* keys.

Any piece of wire that is powered is said to have value '1.' Any piece of wire that is *not* powered is said to have value '0.'

The values of the wire in a loop as described previously are a special case of these rules for assigning values to wires.

#### **Normally Closed Relay**

#### **Normally Closed Relay Diagram**

The preceding picture and diagram show a bottom key that controls an electromagnet. The *electromagnet*, in turn, controls the *top*, *normally closed key*. A normally closed key and the electromagnet that controls it are, *together*, called a normally closed relay.

When the bottom key is pressed, the electromagnet is powered and the electromagnet becomes magnetic. That makes the electromagnet attract the top, normally closed key and pull the top, normally closed key down, just like a finger can push a normally closed key down. A magnet (or a powered electromagnet) attracts the normally closed key because the normally closed key is made of steel. When the bottom key is pressed, the light turns *off*.

In other words, when the bottom key is pressed, the electromagnet energizes, disconnecting the top key.

#### **Clear Key** normally open normally closed loop key clear key middle power wire wire battery electro- $\operatorname{ground} \mathbf{7}$ magnet wire loop wire -**Clear Key Diagram** normally open top of loop key middle battery power wire wire normally closed clear key electromagnet loop wire.

The picture and diagram above show a loop as before, but a normally closed key has been added. As long as the normally closed key is closed, the loop works as before.

However, if the normally closed key is pressed, then the normally closed key will be open and electricity will not reach the electromagnet, so the electromagnet will not be magnetic, and the normally open key will pop up if it was down. If the normally open key already was up, it will stay up.

Therefore, pressing the normally closed key will clear the value of the loop to '0.' Therefore, this normally closed key is called the 'clear key' for the loop.

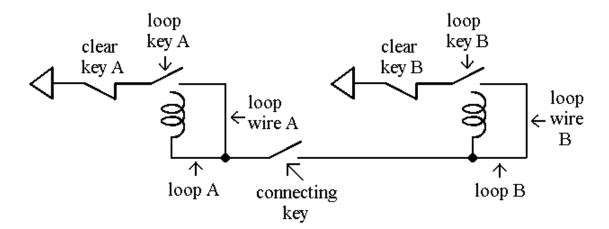

#### **Loop to Loop Data Transfer**

In the circuit above, the 'connecting key' connects loop A and loop B. Both loops have value 0. Temporarily pressing 'loop key A' gives the value 1 to loop A. Now, temporarily pressing the 'connecting key' will make loop B have value 1. That is because when loop A has value 1, loop key A is closed, loop wire A has value 1, and when the connecting key is closed, electricity can reach the electromagnet of loop B, giving loop B value 1.

However, if loop A has value 0, and loop B has value 0, and the connecting key is pressed, then both loops keep their values of 0.

Therefore, if one temporarily presses 'clear key B' to clear loop B to value 0, and then temporarily presses the connecting key, whatever value is in loop A will be copied to loop B. Then loop A and loop B will have the same value.

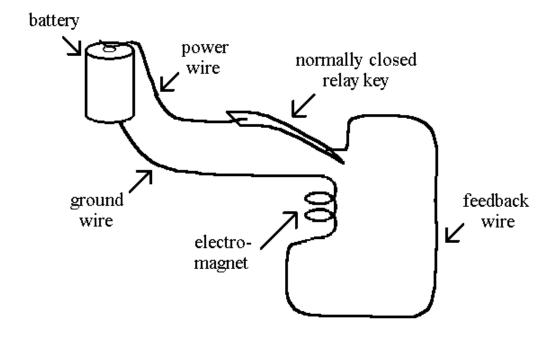

#### **Oscillator**

#### **Oscillator Diagram**

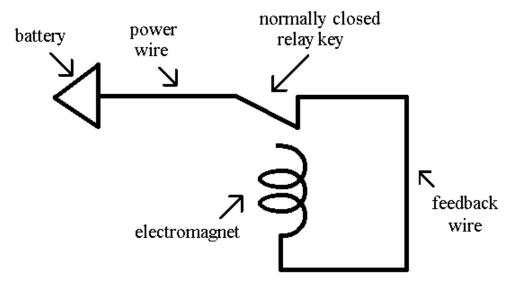

The picture and diagram at left show a normally closed relay that controls its *own* electromagnet. The square of wire that takes electricity from the normally closed key of the relay to the electromagnet of the same normally closed relay is called a feedback wire. (Notice that this circuit is different from a loop circuit, which uses a normally open relay.) This circuit is called an oscillator because the relay oscillates (changes back and forth) between open and closed.

Electricity can get from the top of the battery, through the *closed*, normally closed relay key to the electromagnet. The electromagnet then pulls the normally closed key down and *opens* the normally closed key. Because the normally closed key is now open, no electricity can get to the electromagnet. The electromagnet now no longer attracts the normally closed key and the normally closed key closes.

Thus, the normally closed key repeatedly opens and closes without anyone touching the key. The feedback wire gets value 1, then value 0, then value 1, etc. It takes a relay about a hundredth of a second to change values.

Just as a normal loop is the basis of a computer memory, this feedback circuit is a key part of a computer's clock. A computer's clock is a circuit that repeatedly generates signals (1 and 0 values).

#### **Keys in Series**

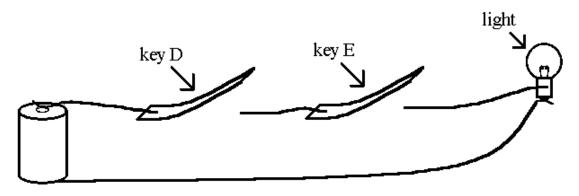

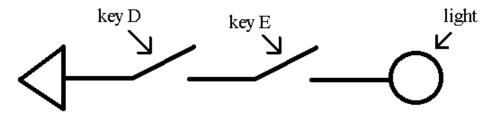

#### **Keys in Series Diagram**

In the picture and diagram above, one must press both 'key D' AND 'key E' to turn the light on.

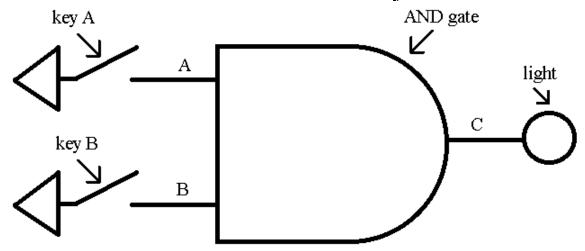

#### **AND Gate Circuit**

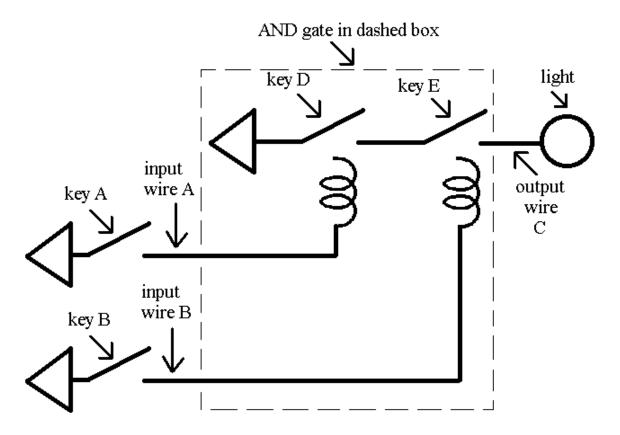

In the circuit above, the three triangles are all the top of the *same* battery. When 'key D' AND 'key E' close, then the light comes on. When 'key A' is pressed, then 'key D' closes. When 'key B' is pressed, then 'key E' closes. Therefore, when 'key A' and 'key B' are pressed, the light turns on. Another way of describing the operation of the circuit is to say that 'output wire C' gets value 1 only when 'input wire A' gets value 1 AND 'input wire B' gets value 1.

The following table also shows that 'output wire C' has value 1 only when both 'input wire A' has value 1 AND 'input wire B' has value 1.

| AND gate truth table |   |   |

|----------------------|---|---|

| Α                    | В | С |

| 0                    | 0 | 0 |

| 0                    | 1 | 0 |

| 1                    | 0 | 0 |

| 1                    | 1 | 1 |

#### **AND Gate Circuit with Symbol**

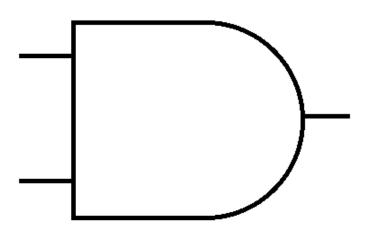

The diagram above shows a circuit with the symbol for an 'AND gate' which is shown, alone, below.

#### **AND Gate Symbol**

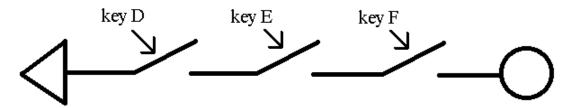

The light in the circuit below only comes on whey key D, key E, AND key F are *all* pressed.

#### Three Keys in Series

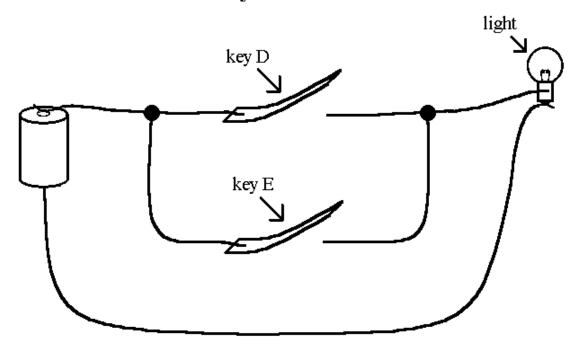

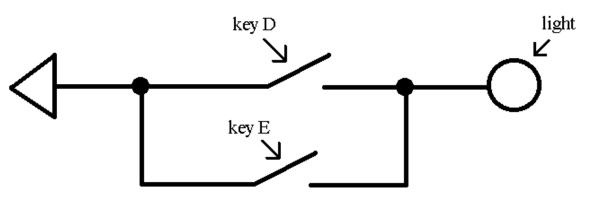

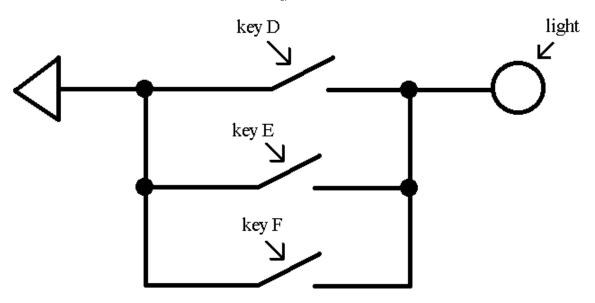

#### **Keys in Parallel**

#### **Keys in Parallel Diagram**

In the picture and diagram above, one need only press either 'key D' OR 'key E' (or both) to turn the light on.

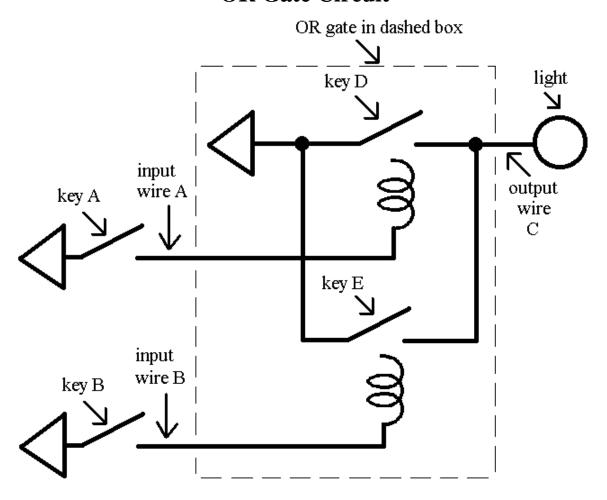

#### **OR Gate Circuit**

In the circuit above, as always, the *crossing wires do not touch* and are *not* connected to each other. When 'key D' OR 'key E' (or both) closes, the light comes on. When 'key A' is pressed, then 'key D' closes. When 'key B' is pressed, then 'key E' closes. Therefore, when 'key A' OR 'key B' is pressed, the light turns on. Another way of describing the operation of this circuit is to say that 'output wire C' gets value 1 only when 'input wire A' has value 1 OR 'input wire B' has value 1.

The following table also shows that 'output wire C' gets value 1 only when either 'input value A' has value 1 OR 'input wire B' has value 1.

| OR gate truth table |   |   |

|---------------------|---|---|

| A                   | В | C |

| 0                   | 0 | 0 |

| 0                   | 1 | 1 |

| 1                   | 0 | 1 |

| 1                   | 1 | 1 |

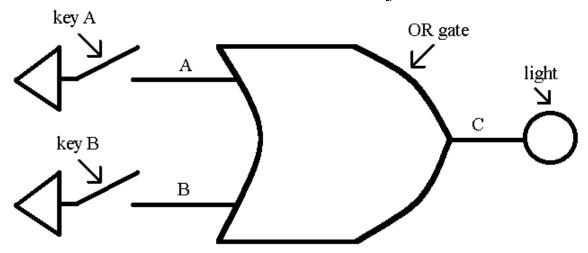

#### **OR Gate Circuit with Symbol**

The diagram above shows a circuit with the symbol for an 'OR gate' which is shown alone, below.

#### **OR Gate Symbol**

#### Three Keys in Parallel

The light in the circuit above turns on when key D, key E, OR key F is pressed.

# **Normally Closed Key**

# **Normally Closed Key Diagram**

In the picture and diagram above, the light is on, as we have seen before. One must press the normally closed key D down to turn the light *off*.

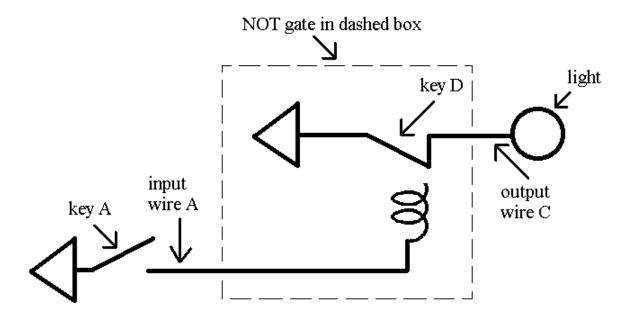

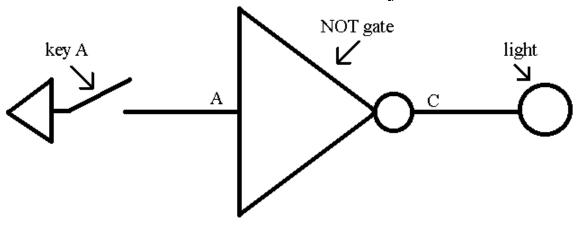

#### **NOT Gate Circuit**

In the circuit above, the triangles are both the top of the *same* battery. When 'key A' is pressed, 'key D' is pulled down and the light goes *off*. That is, when 'key A' is pressed, normally closed 'key D' opens. Therefore, when 'key A' is pressed, the light goes *off*. Another way of describing the operation of the circuit is to say that 'output wire C' gets value 0 when 'input wire A' gets value 1. 'Output wire C' gets value 1 when 'input wire A' gets value 0.

The following table also shows that 'output wire C' gets value 0 only when 'input wire A' gets value 1.

| NOT gate truth table |   |  |  |

|----------------------|---|--|--|

| A                    | С |  |  |

| 0                    | 1 |  |  |

| 1                    | 0 |  |  |

## **NOT Gate Circuit with Symbol**

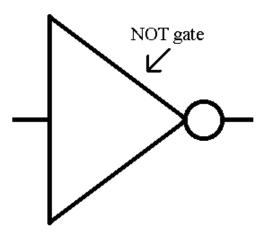

The diagram above shows a circuit with the symbol for a 'NOT gate' which is shown alone, below.

## **NOT Gate Symbol**

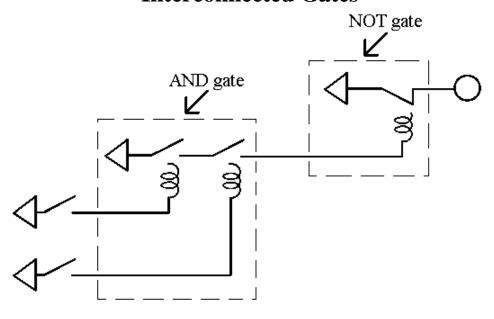

#### **Interconnected Gates**

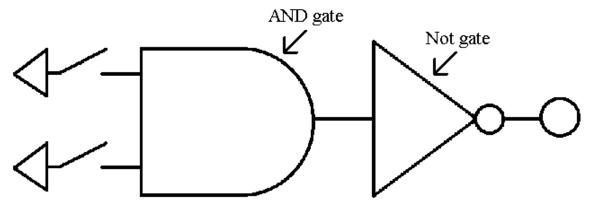

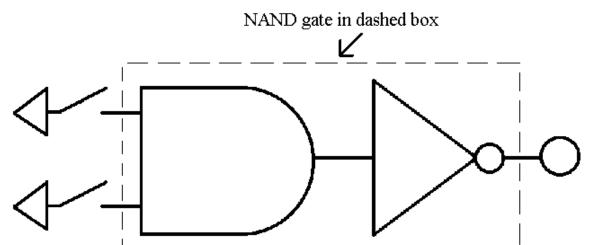

The diagram above shows that the output of an AND gate can be the input for a NOT gate. The circuit above can also be represented with gate symbols as below.

#### **Interconnected Gates with Symbols**

A 'NAND gate' can be constructed from an AND gate followed by a NOT gate as indicated below.

#### **Constructed NAND Gate**

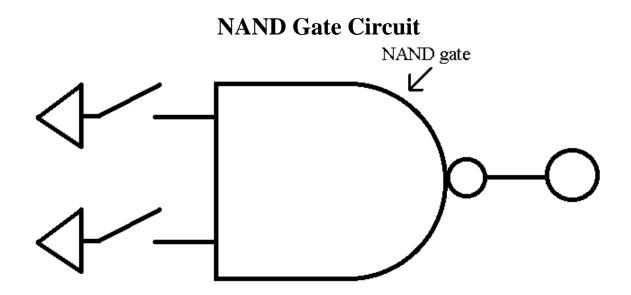

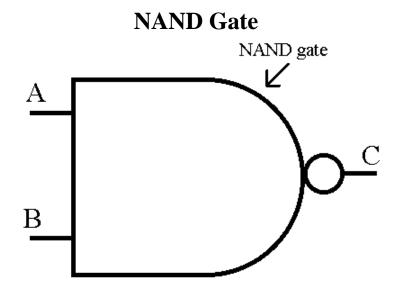

A NAND gate can be represented by the single symbol in the circuit below.

A lone NAND gate is pictured below.

The truth table for the NAND gate is shown below.

| NAND gate truth table |   |   |  |  |

|-----------------------|---|---|--|--|

| A                     | В | C |  |  |

| 0                     | 0 | 1 |  |  |

| 0                     | 1 | 1 |  |  |

| 1                     | 0 | 1 |  |  |

| 1                     | 1 | 0 |  |  |

# **MEMORY**

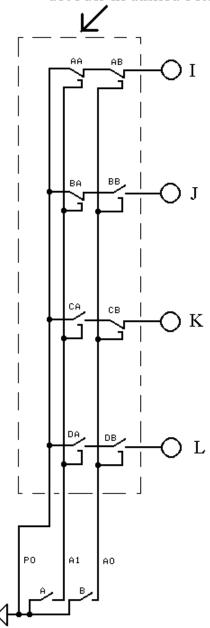

# (Address) Decoder

decoder in dashed box

The diagram at left shows a 'decoder.' A and B are the inputs to the decoder and I, J, K, and L are the outputs. The truth table for this circuit is shown below.

| A | В | I | J | K | L |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

Normally closed relay AA is closed. Normally closed relay AB is also closed. Therefore, electricity can travel from the top of the battery, through AA and AB, to light I.

If keys A and B are both pressed, then normally open relays DA and DB are closed (because their electromagnets are powered) and electricity can reach light L.

Similarly, if key A is pressed and key B is *not* pressed, then normally open relay CA is closed and *normally closed relay* CB is closed and light K is on.

Finally, if key A is *not* pressed and key B is pressed, then light J is on.

Wire PO is power. A1 and A0 are address wire 1 and address wire 0. PO has value 1. A1 can have value 1 or 0, and A0 can have value 1 or 0.

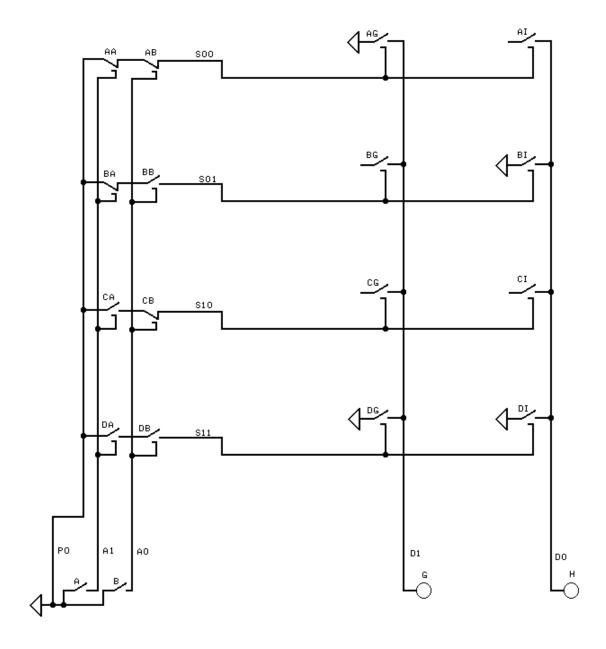

## **Truth Table Generator**

In the preceding circuit, keys A and B are the inputs and lights G and H are the outputs. The truth table for the circuit above is shown below.

| A | В | G | Н |

|---|---|---|---|

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 |

For example, if neither A nor B is pressed, then S00 is powered (has value 1) because the normally closed relays AA and AB are then closed. BB is open so S01 is 0, CA is open so S10 is 0, and both DA and DB are open so S11 is 0. Because S00 is powered, AG is closed and electricity can go from the top of the battery (indicated by a triangle), through relay AG, to wire D1 to light G, so G is on. Relay AI is also closed but relay AI's key is *not* connected to the top of the battery so *no* electricity gets to light H.

For another example, if *both* keys A and B are pressed, then A=1 and B=1 and relays DA and DB are closed. That makes S11=1 and closes relays DG and DI. Electricity can go from the top of the battery through DG and D1 to light G and through DI and D2 to light H. Therefore, A=1 and B=1 results in G=1 and H=1 as in the truth table.

D1 and D0 are data wire 1 and data wire 0. D1 can have value 1 or 0 and D0 can be 1 or 0.

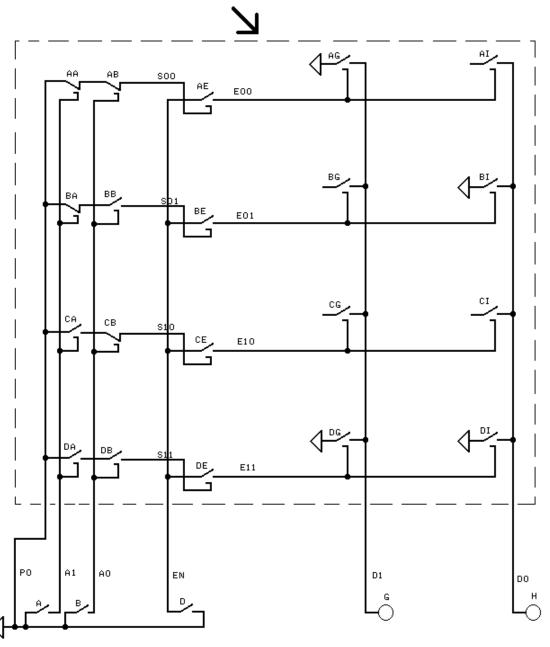

## ROM (Read-Only Memory) With Enable (EN) Key (D)

ROM in dashed box

The circuit above has the following truth table:

| EN | A1 | A0 | D1 | D0 |

|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  |

| 0  | 0  | 1  | 0  | 0  |

| 0  | 1  | 0  | 0  | 0  |

| 0  | 1  | 1  | 0  | 0  |

| 1  | 0  | 0  | 1  | 0  |

| 1  | 0  | 1  | 0  | 1  |

| 1  | 1  | 0  | 0  | 0  |

| 1  | 1  | 1  | 1  | 1  |

If key D (EN) is *not* pressed ('EN' stands for 'enable.'), then EN is 0, so *no* electricity gets to the electromagnets of AG and AI. Similarly, BG, BI, CG, CI, DG, and DI are open if D (EN) is *not* pressed. Therefore, if D (EN) is *not* pressed, then *no* electricity can get to lights G and H as indicated in the truth table.

If A and B are *not* pressed (A1=0 and A0=0), then electricity gets to the electromagnet of AE and closes relay AE. If D is then pressed (EN=1), then electricity can go from the top of the battery, through D and through AE to the electromagnets of AG and AI. AG and AI then close and electricity can go from the top of the battery, through AG, to wire D1 and light G.

The truth table above can also be represented as below.

| EN | A1 | A0 | D1 | D0 |

|----|----|----|----|----|

| 0  | X  | X  | 0  | 0  |

| 1  | 0  | 0  | 1  | 0  |

| 1  | 0  | 1  | 0  | 1  |

| 1  | 1  | 0  | 0  | 0  |

| 1  | 1  | 1  | 1  | 1  |

The X's mean 0 or 1. That is, the row with X's means that if EN is 0, then D1=0 and D0=0 no matter what values A1 and A0 have.

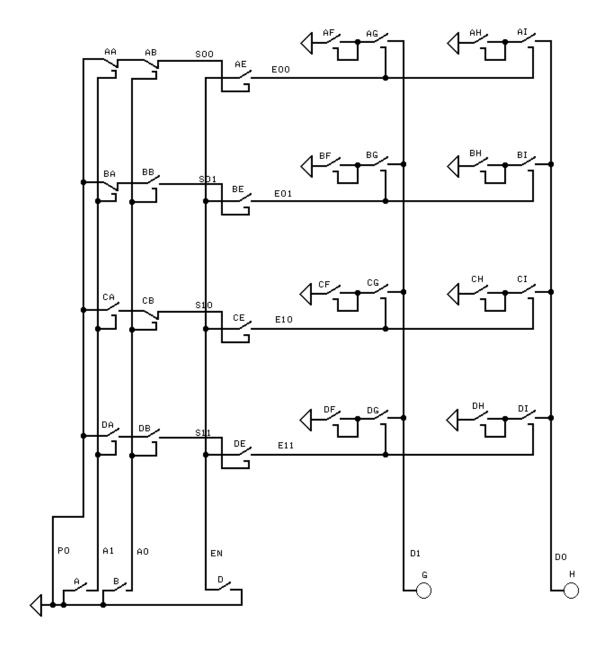

# **Loops Added**

In the circuit above, eight loops have been added to the previous circuit. The loops are labeled AF, AH, BF, BH, CF, CH, DF, and DH. Each loop can have value 0 or 1. The truth table fore this circuit is shown below.

| EN | A1 | A0 | D1 | D0 |

|----|----|----|----|----|

| 0  | X  | X  | 0  | 0  |

| 1  | 0  | 0  | AF | AH |

| 1  | 0  | 1  | BF | ВН |

| 1  | 1  | 0  | CF | СН |

| 1  | 1  | 1  | DF | DH |

To make loop AF have value 1, just press key AF down. Key AF will stay down because it is part of a loop. To make AF have value 0 again, just lift key AF up. It will stay up on its own. In the truth table, 'AF' means the value of loop AF. The other loops, AH, BF, BH, CF, CH, DF, and DH, operate similarly.

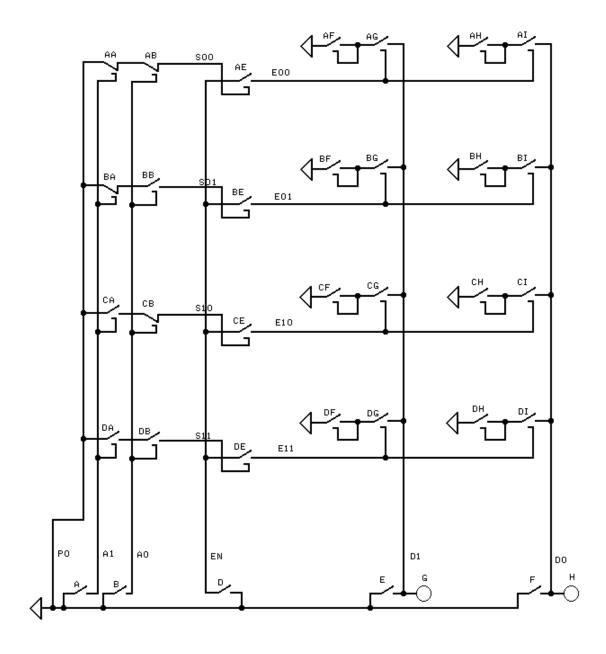

# **Input Keys Added**

In the diagram at left, key E and key F (bottom right) have been added to the circuit. Keys E and F allow one to set a loop to value 1 without touching the loop's key.

For example, to set loop AF to 1 without touching key AF, one must *not* push key A or key B, which closes relay AE. Then you hold down key E to put value 1 on wire D1. Finally, temporarily pushing key D makes EN temporarily 1. Because AE is closed, EN=1 powers relay AG's electromagnet and closes AG. D1's value of 1 can now go through key AG to loop AF, thereby making loop AF have value 1.

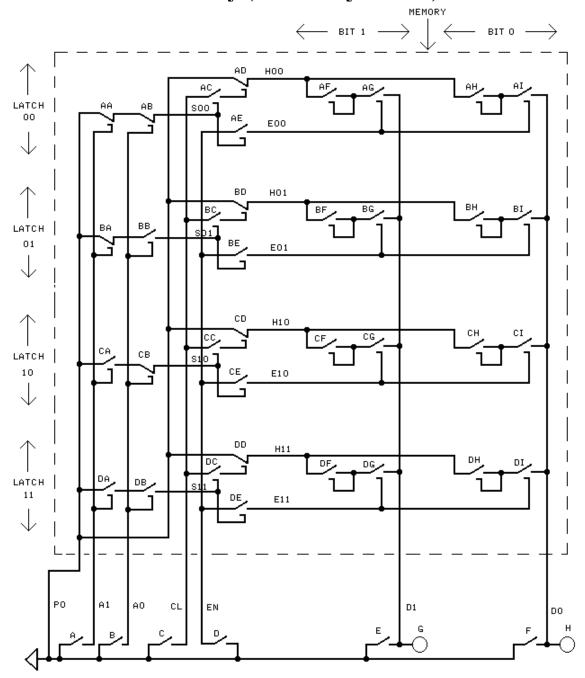

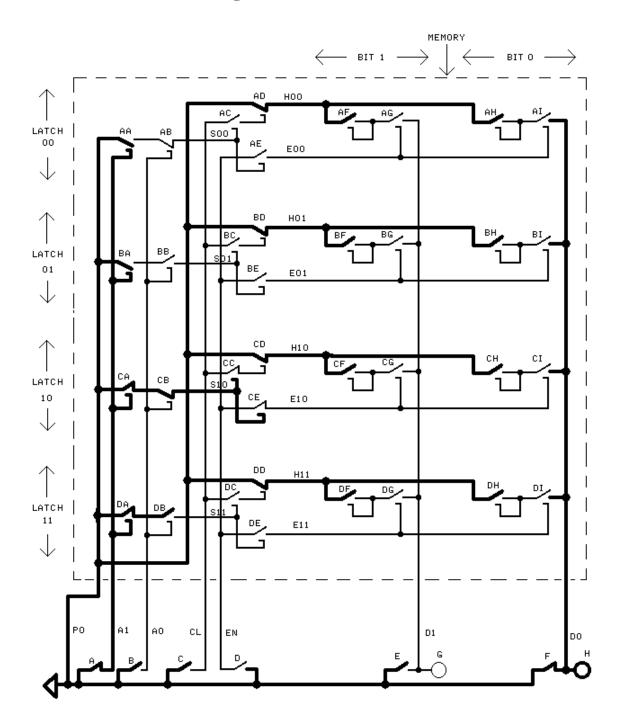

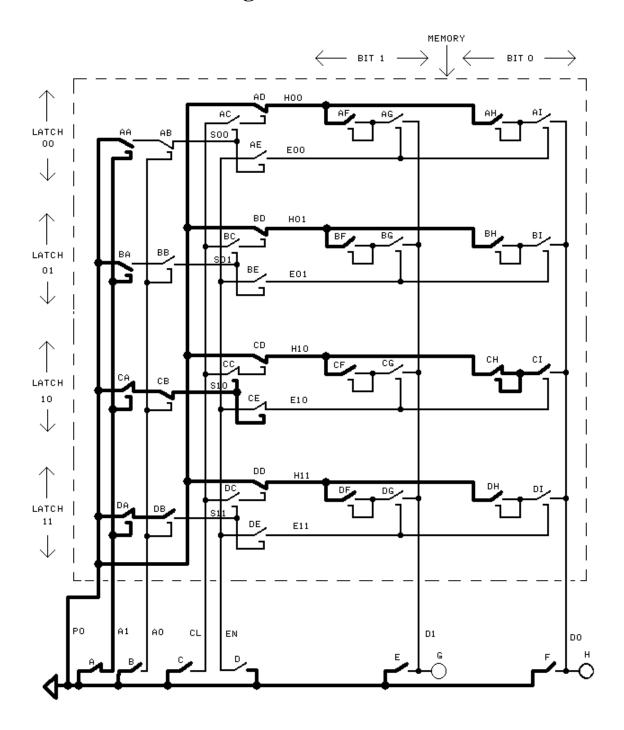

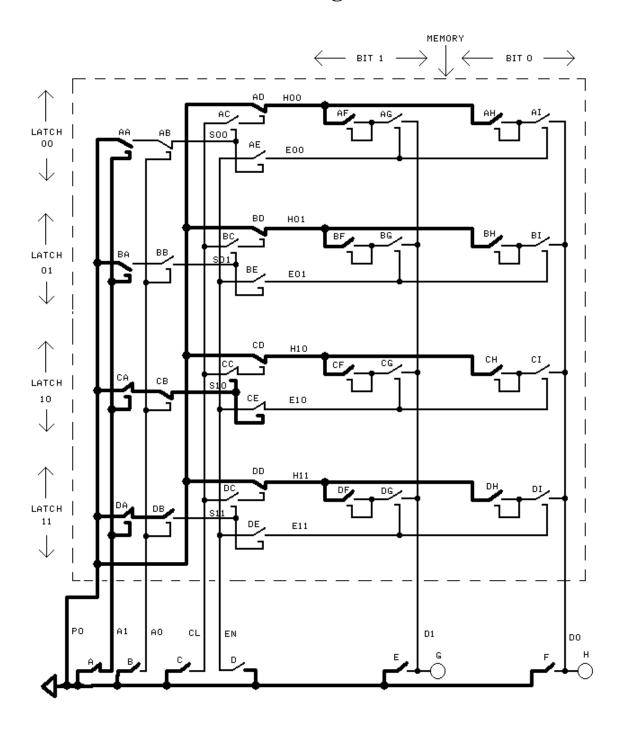

# **Memory (Clear Key Added)**

In this circuit, key C, wire CL (for CLear), relays AC, BC, CC, and DC, normally closed relays AD, BD, CD, and DD, and wires H00, H01, H10 and H11 (H for Hold, or remember) have been added to the circuit. These additions allow loops to be 'cleared' to value 0 by manipulating keys outside the dashed box (memory) without touching the loop keys.

The diagram above shows a *memory* within the dashed box. The memory can be controlled by the keys outside the dashed box at the bottom of the diagram. What a memory does will be explained first. Then, *how* the memory works will be described.

AF, AH, BF, BH, CF, CH, DF, and DH are each relay keys of loops. You can change the value of loop AF from 0 to 1 by simply pressing key AF down. Similarly, you can change the value of loop AF from 1 to 0 by lifting key AF. To determine whether a loop has value 0 or value 1, just look at the loop's key. If the key is down, then the loop has value 1. If the key is up, then the loop has value 0. The value of a loop stays the same until you change it.

However, suppose that the dashed box was a physical box and you could not reach inside the box. If you buy a memory chip at a store, the circuitry is enclosed in a plastic box with wires PO, A1, A0, CL (This may be called WR for 'WRite.'), EN, D1, D0 and *GRound wire*, GR, sticking out. The circuitry uses transistors instead of relays for switches, so even if you broke the box open, you couldn't change the values by hand. (A memory from a store would probably have more address lines (wires) like A2, A3, ... A20 and data lines like D2, D3, ... D7.)

The memory is constructed so that the values in the loops can be examined and changed using only keys A, B, C, D, E, and F and light bulbs G and H which are all outside the box and are *not* part of the memory.

## Where Power Reaches in a Memory

The **bold** wires in the diagram at left, show which wires are powered.

A wire is powered only if it is connected to the top of the battery (represented by a triangle in the lower left corner of the diagram, as shown below).

Notice the new symbol used for keys AC and AE. Keys AC and AE are *normally open keys*. However, they are *closed now* because their electromagnets are powered. Therefore, they are represented as:

instead of as:

Electricity can flow from left to right (or right to left) through a closed key even if it's a closed but *normally open key*.

Similarly, an open, normally closed key is represented as:

## open, normally closed key

\_\_\_\_

instead of as:

closed, normally closed key

Notice that, in the diagram of memory, all of the loops (AF, AH, BF, BH, CF, CH, DF, and DH) have value 0 because all of those normally open keys are *open*.

AF is 'bit 1' of 'latch 00' and has value 0. AH is bit 0 of latch 00 and also has value 0.

You should follow the power from the top of the battery (the triangle in the lower left of the diagram of memory *above*) and see why certain wires are *bold* and the rest are normal. Remember, electricity *can't* go through *open* keys. Electricity also does *not* travel between *crossing wires*. Crossing wires are *not* touching (not connected). You should also understand why some electromagnets are powered and others aren't, and how powering the electromagnet of a key *closes* a *normally open key* and, in later diagrams, *opens* a *normally closed key*.

Now, suppose we want to store value 01 in latch 10. This means we want to keep key CF *open* for value 0 and *close* key CH for value 1. This is called 'writing' value 01 to address 10.

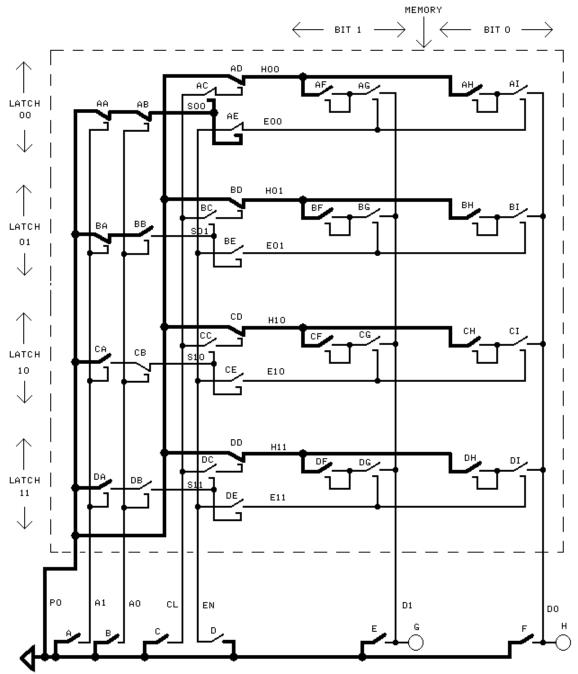

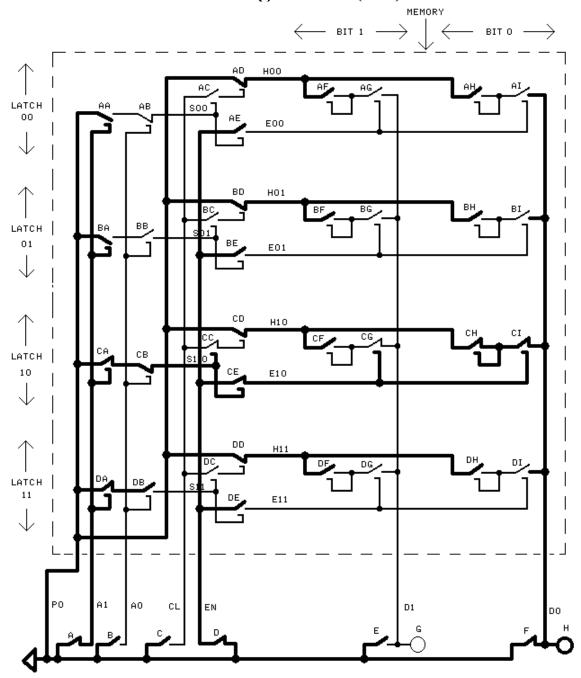

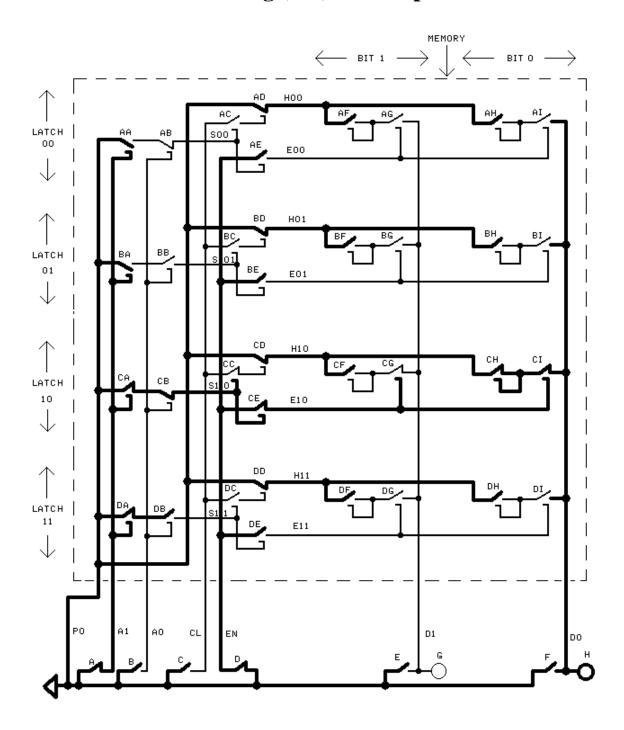

To do this, you *first* select latch 10 by pressing key A and *not* pressing key B. This selects latch 10 as indicated by the *bold* select 10 wire, 'S10,' in the diagram *below*. Key A controls address wire 1, labeled A1 in the diagram, and key B controls address wire 0, labeled A0 in the diagram. Both address wires, A1 and A0, together, are called the address bus. A group of similar wires are, together, called a 'bus.' Pressing key A and *not* pressing key B results in power going through the circuit as indicated by *bold lines* in the diagram below. Notice that horizontal wire S10 has power (is bold) while S00, S01, and S11 do *not* have power. This selects latch 10.

# **Selecting the Address**

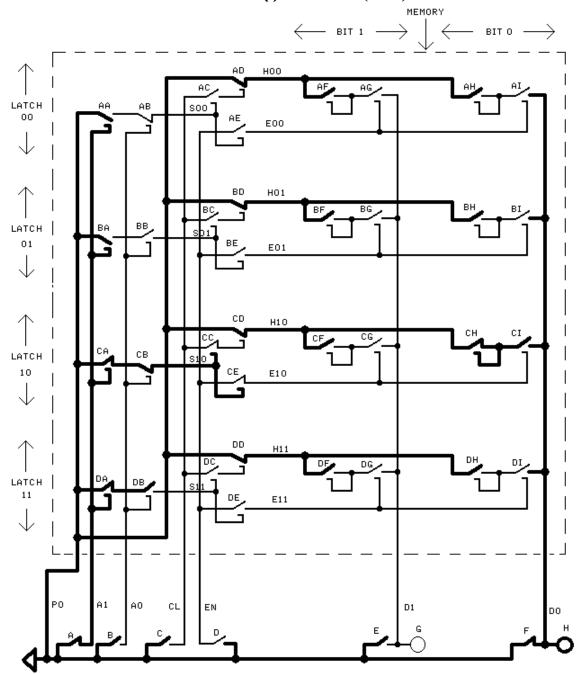

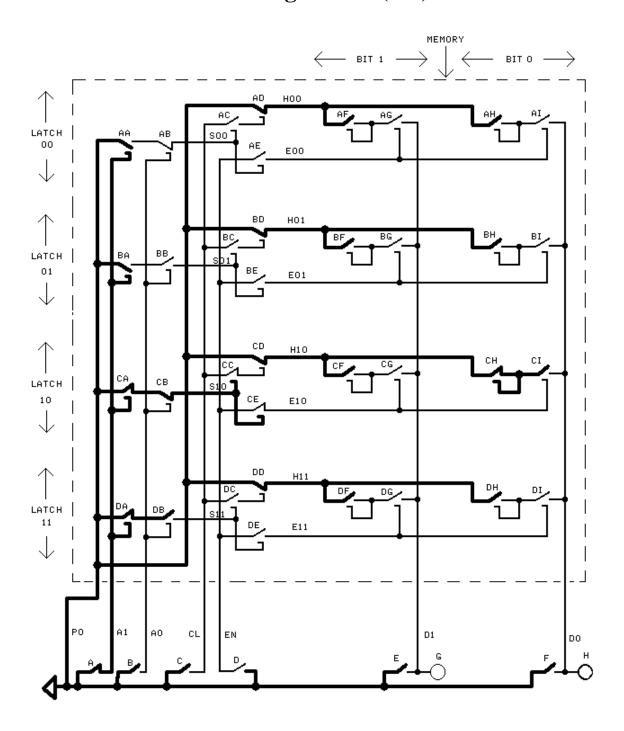

The *second* step in writing value 01 to address (latch) 10 is to press key F and *not* press key E as in the following diagram. *Not* pressing key E gives value 0 to data wire D1 and *pressing* key F gives value 1 to data wire D0. Both data wires, D1 and D0, are, together, called the 'data bus' just as both address wires, A1 and A0, are, together, called the 'address bus.' The first and second steps can be done simultaneously. This results in power going through the circuit as indicated by the *bold* wires in the diagram below. Wire D0 is bold and, so, has value 1.

# **Selecting the Data to be Written**

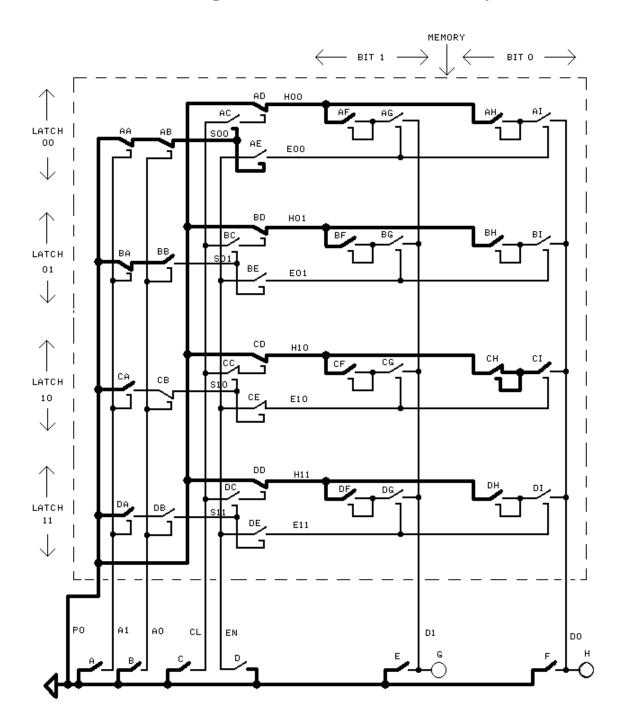

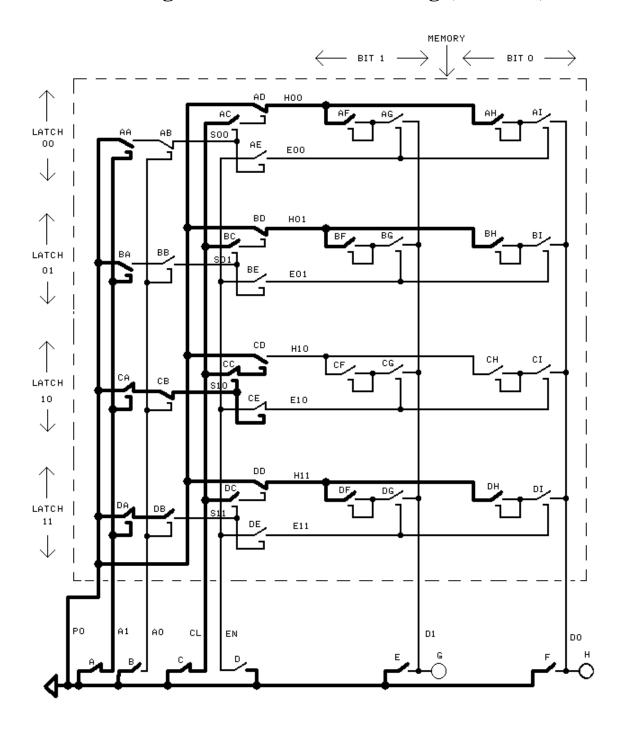

The *third* step in writing 01 to address 10 is pressing the enable key, 'D,' which controls the enable ('EN') wire. This results in power going through the circuit as indicated in bold in the following diagram. Notice that *loop* CH now has value 1. Loop CH got power from wire D0 through CI. *No* power went from wire D1 through CG to loop CF because wire D1 is *not* powered.

It's important to remember that pressing the enable key, 'D,' makes EN=1 and connects the loops of the selected (by the address wires A1 and A0) latch to the data bus wires, D1 and D0.

# **Pressing Enable (EN)**

In the fourth step, key D is released and the enable (EN) wire returns to value 0 (unpowered). This results in power flowing through the memory as indicated by bold wires in the following diagram. Notice that loop CH still has value 1 even though loop CH is no longer connected to data wire D0 through relay CI (because relay CI is open).

# **Releasing Enable (EN)**

Step five: Keys A and F are released and address *wire* A0 and data *wire* D0 get value 0 (as indicated in the following diagram). Notice that *loop CH still has value 1*.

Therefore, to write value 01 to latch 10, you press A and *not* B to select latch 10; and, to choose data 01, do *not* push E and push F. This makes wire A1 have value 1, wire A0 have value 0, wire D1 have value 0, and wire D0 have value 1. Then, while holding A and F down, temporarily press D to make the enable wire, EN, temporarily 1. Then, release A and F. This can be described as follows.

- 1. Select the address and data with the address and data keys A, B, E, and F (A1, A0, D1 and D0).

- 2. Temporarily press D (EN).

- 3. Release the address and data keys.

That's all there is to storing data in an *empty* latch.

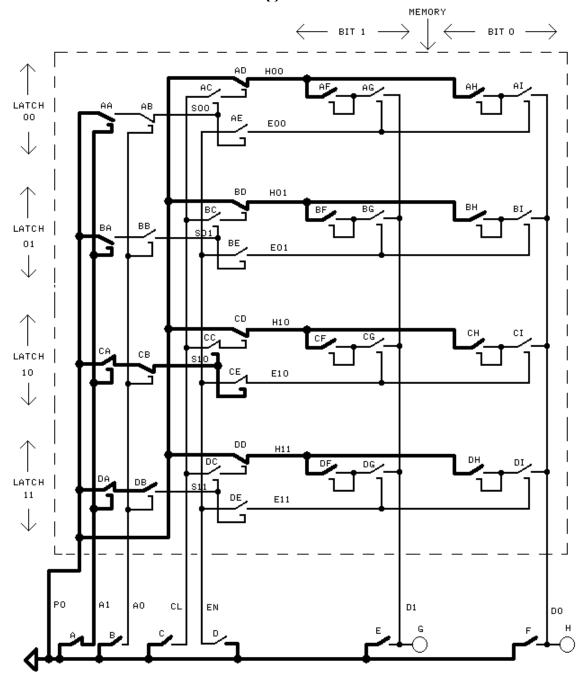

# **Releasing the Address and Data Keys**

To find out what is in a latch, do the following.

- 1. Select the address of the latch you want to read with keys A (wire A1) and B (wire A0).

- 2. Press key 'D' to make the 'EN' wire have value 1. The lights G and H will indicate the values of the data bits stored in that latch.

- 3. Release the enable key D.

- 4. Release the address keys, A and B.

For example, to read latch 10, *first* press key A (and *not* key B) to select latch 10 (as indicated in the following diagram).

# **Selecting the Address to Read**

*Second*, press key D to make the enable (EN) wire have value 1. Then light H comes on indicating that bit 0 of latch 10 has value 1 and light G stays off indicating that latch 10 has value 0 in bit 1. This is shown in the following diagram.

Notice that making wire EN have value 1 connects the loops of the selected latch to the data wires D1 and D0.

## **Enabling (EN) the Output**

*Third*, release key D when done reading latch 10 (as indicated in the following diagram). That's all there is to reading a latch in memory.

## **Releasing Enable (EN)**

To *erase* a value from a latch and make all of the latch's loops have value 0, do the following.

- 1. Select the latch with keys A (A1) and B (A0).

- 2. Temporarily press key C to make the 'clear' (CL) wire temporarily have value 1.

The following diagram shows latch 10 selected by pressing A and *not* pressing key B. It also shows key C being pressed to clear both of latch 10's data bits to 0. Don't press C until after A is pressed (so that no other latch is accidentally erased).

Notice that pressing C makes the selected 'H' (for 'Hold') wire, 'H10,' have value 0.

## **Selecting the Address and Clearing (with CL)**

Release key CL after clearing latch 10 as indicated in the following diagram. Don't release key A until *after* CL is released so that you don't accidentally erase another latch.

Writing to a latch will *not* clear *any* bits that were previously 1, so *always* clear a latch before copying (writing) data to it. Therefore, to write to a latch, do the following.

- 1. Press the correct address keys (A and B) and data keys (E and F).

- 2. Press the clear key, C, to clear the latch.

- 3. Release the clear key, C.

- 4. Press the enable key, D, to send data from the data wires (D1 and D0) to the latch.

- 5. Release the enable key, D.

- 6. Release the address keys (A and B) and the data keys (E and F).

To read data, just do the following.

- 1. Press the correct address keys, A and B, to select the latch to read.

- 2. Press the enable key, D, to send the latch's values to the lights, G and H.

- 3. Release the enable key D.

- 4. Release the address keys, A and B.

## **Releasing CL**

The memory in the drawings is very small. There are only two address wires and two data wires. Because there are two address wires, there are four possible addresses: 00, 01, 10, and 11, and, so, four latches. Because there are two data wires, each latch has two loops. Each loop holds one 'bit' of information, a 0 or a 1. Four latches with two loops each means  $8 (= 4 \times 2)$  loops total.

The table below shows all bit values in each latch when data 01 has been written to the loops of latch 10.

| latch   | bit    |

|---------|--------|

| address | values |

| 00      | 00     |

| 01      | 00     |

| 10      | 01     |

| 11      | 00     |

A larger memory with *four* address bits and *four* data bits with 0 in all the loops can be represented as below.

| latch   | bit    |

|---------|--------|

| address | values |

| 0000    | 0000   |

| 0001    | 0000   |

| 0010    | 0000   |

| 0011    | 0000   |

| 0100    | 0000   |

| 0101    | 0000   |

| 0110    | 0000   |

| 0111    | 0000   |

| 1000    | 0000   |

| 1001    | 0000   |

| 1010    | 0000   |

| 1011    | 0000   |

| 1100    | 0000   |

| 1101    | 0000   |

| 1110    | 0000   |

| 1111    | 0000   |

# **INSTRUCTIONS**

The next most important part of a computer, after memory, is the processor. A processor changes the values in memory as instructed by instructions stored in memory. An instruction is a group of bits (loop values) in memory that tell the processor to do something. A group of instructions that instruct the processor to do some task is called a program.

The simple kind of processor described in this book has only one type of instruction, but that instruction is sufficient to do anything, as will be seen. The instruction is 'copy' (and 'go to'). Each instruction simply copies some bits of data from somewhere in one latch in memory to somewhere else in another latch in memory. The instruction indicates:

- 1. which latch to copy data (data is bit (loop) values) from

- 2. which latch to copy data to

- 3. which bits to change in the copied-to latch

- 4. how much to rotate the 'from' data before copying some of its bits to the 'to' data latch

- 5. which latches to get the next instruction from.

In the computer considered here, the number of address bits is the same as the number of data bits.

The explanation of the following example will not be clear at first, but just read through it. Then reread it. It will be clear later.

Consider a four-address-bit, four-data-bit memory with the values (in loops) below:

#### **Example Program**

|               | latch        | bit          |                                |

|---------------|--------------|--------------|--------------------------------|

| i             | address      | value        | s                              |

|               | 0000         | 0100         | address of instruction         |

|               | 0001         | 000 <u>1</u> | value of a                     |

|               | 001 <i>0</i> | 000 <u>1</u> | $not 0 = \underline{1}$        |

|               | 0011         | 000 <u>0</u> | not 1 = 0                      |

| instruction_1 | 0100         | 0001         | from address                   |

|               | 0101         | 1000         | to address                     |

|               | 0110         | 0001         | <pre>`to' bits to change</pre> |

|               | 0111         | 10 <u>00</u> | instr.addr.and rot.amount      |

| instruction_2 | 1000         | 0010         | from address                   |

| _             | 1001         | 0001         | to address                     |

|               | 1010         | 0001         | <pre>`to' bits to change</pre> |

|               | 1011         | 11 <u>00</u> | instr.addr.and rot.amount      |

| instruction_3 | 1100         | 0000         | from address                   |

| _             | 1101         | 0000         | to address                     |

|               | 1110         | 0000         | <pre>`to' bits to change</pre> |

|               | 1111         | 11 <u>00</u> | instr.addr.and rot.amount      |

|               |              |              |                                |

Only the 1's and 0's are part of the program. The rest is just comments for a person. The latch addresses are just where the program is stored. The bit values are the program.

Latch 0000 holds the value  $0\underline{1}00$  so that the first instruction is in latches  $0\underline{1}00$ ,  $0\underline{1}01$ ,  $0\underline{1}10$ , and  $0\underline{1}11$ , and is labeled 'instruction\_1' in the program. Latch 0000 is special and always holds the address of the next instruction to be executed.

The first word of instruction\_1 is in latch <u>01</u>00 and is 0001. That means that data (bit values) is copied *from* latch 0001 in memory.

The second word of instuction\_1 is in latch <u>01</u>01 and is 1000 and indicates that the data will be copied *to* latch 1000.

The third word of instruction\_1 is in latch 0110 and is 0001 and indicates that only the rightmost bit, and *not* the three leftmost bits, of latch 1000 will be changed because only the rightmost bit of 0001 is 1.

The rightmost two bits of latch 0111 are 00 and indicate that the data in latch 0001 will *not* be rotated at all when data is copied to latch 1000.

The leftmost two bits of latch <u>01</u>11 are <u>10</u> and indicate that the next instruction will be in latches <u>10</u>00, <u>10</u>01, <u>10</u>10, and <u>10</u>11. That is, instruction\_2 will be executed next.

<sup>&#</sup>x27;Instr.addr.and rot.amount' is short for 'next instruction's address and rotate amount.'

After instruction\_1 is executed, the memory has the following bit values.

| late              | h bit          |     |                                      |

|-------------------|----------------|-----|--------------------------------------|

| addres            | s valu         | es  |                                      |

| 000               | 00 1000        | <   | address of instruction               |

| 000               | 0001           |     | value of a                           |

| 000               | 0001           |     | not 0 = 1                            |

| 000               | 1 0000         |     | not 1 = 0                            |

| instruction_1 010 | 0001           |     | from address                         |

| 010               | 1000           |     | to address                           |

| 01:               | 0001           | 1 1 | <pre>`to' bits to change</pre>       |

| 013               | 1000           | +   | <pre>instr.addr.and rot.amount</pre> |

| instruction_2 100 | 0 001 <u>1</u> | <   | from address                         |

| 100               | 0001           |     | to address                           |

| 10:               | 0001           |     | <pre>`to' bits to change</pre>       |

| 10:               | 1100           |     | <pre>instr.addr.and rot.amount</pre> |

| instruction_3 110 | 0000           |     | from address                         |

|                   | 0000           |     | to address                           |

| 11:               | 0000           |     | <pre>`to' bits to change</pre>       |

| 11:               | 1100           |     | <pre>instr.addr.and rot.amount</pre> |

The underlined loop values (bits) were copied to when instruction\_1 was executed. The *italics* show from where data was copied. The arrows show how data was copied. The rightmost bit of latch 0001 has been copied to the rightmost bit of latch 1000. Also, all bits of latch 0111 (that is,  $\underline{1000}$ ) have been copied to latch 0000 indicating that the next instruction will be in latches  $\underline{1000}$ ,  $\underline{1001}$ ,  $\underline{1010}$ , and  $\underline{1011}$  (instruction\_2). That is, after the first instruction, instruction\_1, is executed, latch 0000 has value  $\underline{1000}$ .

The leftmost two bits of latch 0000 are 10, so the instruction executed next is instruction\_2, in latches 1000, 1001, 1010, and 1011.

- 1. Latch 1000 holds 0011, so data is copied from latch 0011.

- 2. Latch 1001 holds 0001, so data is copied to latch 0001.

- 3. Latch 1010 holds 0001, so only the rightmost bit of the 'to latch,' latch 0001, is copied to.

- 4. Latch 1011 holds 1100. The rightmost two bits of 1100 are 00 so the data copied from is *not* rotated at all. The leftmost two bits of 1100 are 11, so the next instruction to be executed will be in latches 1100, 1101, 1110, and 1111 (instruction\_3).

After instruction\_2 is executed, the memory has the following bit values.

| latch<br>address   | bit<br>values  |                                |

|--------------------|----------------|--------------------------------|

| 0000               | <u>1100</u> <  | address of instruction         |

| 0001               | 000 <u>0</u> < | value of a                     |

| 0010               | 0001           | not 0 = 1                      |

| 0011               | 0000           | not 1 = 0                      |

| instruction_1 0100 | 0001           | from address                   |

| 0101               | 1000           | to address                     |

| 0110               | 0001           | <pre>`to' bits to change</pre> |

| 0111               | 1000           | instr.addr.and rot.amount      |

| instruction_2 1000 | 0011           | from address                   |

| 1001               | 0001           | to address                     |

| 1010               | 0001           | <pre>`to' bits to change</pre> |

| 1011               | 1100           | instr.addr.and rot.amount      |

| instruction_3 1100 | 0000           | from address                   |

| 1101               | 0000           | to address                     |

| 1110               | 0000           | <pre>`to' bits to change</pre> |

| 1111               | 1100           | instr.addr.and rot.amount      |

The italics show from where data was copied. The underlining shows to where data was copied. The arrows show how data was copied.

Latch 0000 now has value 1100, so that the next instruction to be executed is instruction\_3 in latches 1100, 1101, 1110, and 1111.

- 1. Latch 1100 holds 0000, so data will be copied from latch 0000.

- 2. Latch 1101 holds 0000, so data is copied to latch 0000.

- 3. Latch 1110 holds 0000, so no data bits are copied (to latch 0000).

- 4. Latch 1111 holds 1100, so 1100 is copied to latch 0000.

This results in the following bit values in memory.

|               | latch<br>dress | bit<br>value | s |                                |

|---------------|----------------|--------------|---|--------------------------------|

|               | 0000           | 1100         | < | address of instruction         |

|               | 0001           | 0000         | į | value of a                     |

|               | 0010           | 0001         | İ | not 0 = 1                      |

|               | 0011           | 0000         |   | not 1 = 0                      |

| instruction_1 | 0100           | 0001         |   | from address                   |

|               | 0101           | 1000         |   | to address                     |

|               | 0110           | 0001         |   | `to' bits to change            |

|               | 0111           | 1000         |   | instr.addr.and rot.amount      |

| instruction_2 | 1000           | 0011         |   | from address                   |

|               | 1001           | 0001         |   | to address                     |

|               | 1010           | 0001         |   | 'to' bits to change            |

|               | 1011           | 1100         |   | instr.addr.and rot.amount      |

| instruction_3 | 1100           | 0000         |   | from address                   |

|               | 1101           | 0000         |   | to address                     |

|               | 1110           | 0000         |   | <pre>`to' bits to change</pre> |

|               | 1111           | 1100         |   | instr.addr.and rot.amount      |

The underlined bits have been copied to from the italic bits.

Thus, instruction\_3 changes nothing (because latch 0000 already held 1100) and leads to instruction\_3 being executed again and again.

Ending a program with an instruction like instruction\_3 ensures that nothing else will happen after the desired instructions (instruction\_1 and instruction\_2) are executed. It's just something for the computer to do until we stop the processor and look in memory for the results.

We will now look at some two-instruction programs. The first instruction will do something and the second instruction will do nothing. These short computer programs will show what an instruction (of this simple computer) can do.

Instruction\_1 of the following program copies 1111 from latch 0001 to latch 0010. Notice that, because latch 0110 of instruction\_1 holds 1111, all 'to data' bits are copied to. Instruction 2 does nothing over and over.

## **Before Copy 1111 to 0010 for 1111**

|               | latch | bit          |                           |  |

|---------------|-------|--------------|---------------------------|--|

| address       |       | values       |                           |  |

|               | 0000  | 0100         | address of instruction    |  |

|               | 0001  | <u>1111</u>  | from data                 |  |

|               | 0010  | 0000         | to data                   |  |

|               | 0011  | 0000         |                           |  |

| instruction_1 | 0100  | 0001         | from address              |  |

|               | 0101  | 0010         | to address                |  |

|               | 0110  | <u>1111</u>  | 'to' bits to copy to      |  |

|               | 0111  | 10 <u>00</u> | instr.addr.and rot.amount |  |

| instruction_2 | 1000  | 0000         |                           |  |

| _             | 1001  | 0000         |                           |  |

|               | 1010  | 0000         |                           |  |

|               | 1011  | 1000         |                           |  |

|               | 1100  | 0000         |                           |  |

|               | 1101  | 0000         |                           |  |

|               | 1110  | 0000         |                           |  |

|               | 1111  | 0000         |                           |  |

|               |       |              |                           |  |

After instruction\_1 is executed, the memory has the following values.

### After Copy 1111 to 0010 for 1111

```

latch bit

address values

0000 1000 <----| address of instruction

0001 1111 ---

from data

0010 <u>1111</u> <--|

0011 0000

| to data

0100 0001

instruction_1

| from address

| to address

0101 0010

0110 <u>1111</u>

| 'to' bits to copy to

0111 1000 ----- instr.addr.and rot.amount

1000 0000

1001 0000

instruction_2

1010 0000

1011 1000

1100 0000

1101 0000

1110 0000

1111 0000

```

Instruction\_1 of the following program copies 0011 from latch 0001 to latch 0010. Notice that, because latch 0110 of instruction\_1 holds 1111, all 'to' bits are copied to.

## Before Copy 0011 to 0010 for 0011

```

latch bit

address values

0000 0100 address of instruction

0001 <u>0011</u> from data

0010 <u>0000</u>

to data

0011 0000

instruction_1

0100 0001

from address

0101 0010

to address

0110 <u>1111</u>

'to' bits to copy to

0111 1000

instr.addr.and rot.amount

instruction 2

1000 0000

1001

0000

1010 0000

1011 1000

1100 0000

1101 0000

1110 0000

1111 0000

```

After instruction\_1 is executed, the memory has the following values.

## After Copy 0011 to 0010 for 0011

```

latch bit

address values

0000 1000 <----| address of instruction

0001 <u>0011</u> ---| | from data

0010 <u>0011</u> <--|

to data

0011 0000

from address to address

0100 0001

instruction_1

0101 0010

0110 1111 | 'to' bits to copy to

0111 1000 -----| instr.addr.and rot.amount

1000 0000

instruction 2

1001 0000

1010 0000

1011 1000

1100 0000

1101 0000

1110 0000

1111 0000

```

Instruction\_1 of the following program copies the rightmost three bits (111) of 1111 from latch 0001 to latch 0010 for 0111. Notice that, because latch 0110 of instruction\_1 holds 0111, the rightmost three 'to' bits are copied to.

## Before Copy 111 to 0010 for 0111

|                          | latch | bit          |                           |  |

|--------------------------|-------|--------------|---------------------------|--|

| address                  |       | values       |                           |  |

|                          | 0000  | 0100         | address of instruction    |  |

|                          | 0001  | 1 <u>111</u> | from data                 |  |

|                          | 0010  | 0 <u>000</u> | to data                   |  |

|                          | 0011  | 0000         |                           |  |

| instruction_1            | 0100  | 0001         | from address              |  |

|                          | 0101  | 0010         | to address                |  |

|                          | 0110  | <u>0111</u>  | 'to' bits to copy to      |  |

|                          | 0111  | 10 <u>00</u> | instr.addr.and rot.amount |  |

| <pre>instruction_2</pre> | 1000  | 0000         |                           |  |

| _                        | 1001  | 0000         |                           |  |

|                          | 1010  | 0000         |                           |  |

|                          | 1011  | 1000         |                           |  |

|                          | 1100  | 0000         |                           |  |

|                          | 1101  | 0000         |                           |  |

|                          | 1110  | 0000         |                           |  |

|                          | 1111  | 0000         |                           |  |

|                          |       |              |                           |  |

After instruction\_1 is executed, the memory has the following values.

## After Copy 111 to 0010 for 0111

```

latch bit

address values

0000 1000 <----| address of instruction

0001 1111 ---

from data

0010 0<u>111</u> <--|

| to data

0011 0000

0100 0001

from address

instruction_1

0101 0010

| to address

0110 0111

'to' bits to copy to

0111 1000 ----- instr.addr.and rot.amount

1000 0000

instruction 2

1001 0000

1010 0000

1011 1000

1100 0000

1101 0000

1110 0000

1111 0000

```

Instruction\_1 of the following program copies the rightmost three bits (000) of 0000 from latch 0001 to latch 0010 for 1000. Notice that, because latch 0110 of instruction\_1 holds 0111, the rightmost three 'to' bits are copied to.

## Before Copy 000 to 0010 for 1000

|               | latch   | bit          |                           |  |  |

|---------------|---------|--------------|---------------------------|--|--|

|               | address |              | values                    |  |  |

|               | 0000    | 0100         | address of instruction    |  |  |

|               | 0001    | 0 <u>000</u> | from data                 |  |  |

|               | 0010    | 1 <u>111</u> | to data                   |  |  |

|               | 0011    | 0000         |                           |  |  |

| instruction_1 | 0100    | 0001         | from address              |  |  |

|               | 0101    | 0010         | to address                |  |  |

|               | 0110    | <u>0111</u>  | 'to' bits to copy to      |  |  |

|               | 0111    | 10 <u>00</u> | instr.addr.and rot.amount |  |  |

| instruction_2 | 1000    | 0000         |                           |  |  |

| _             | 1001    | 0000         |                           |  |  |

|               | 1010    | 0000         |                           |  |  |

|               | 1011    | 1000         |                           |  |  |

|               | 1100    | 0000         |                           |  |  |

|               | 1101    | 0000         |                           |  |  |

|               | 1110    | 0000         |                           |  |  |

|               | 1111    | 0000         |                           |  |  |

|               |         |              |                           |  |  |

After instruction\_1 is executed, the memory has the following values.

## After Copy 000 to 0010 for 1000

```

latch bit

address values

0000 1000 <----| address of instruction

0001 0<u>000</u> ---|

from data

0010 1<u>000</u> <--|

| to data

0011 0000

0100 0001

from address

instruction_1

0101 0010

| to address

0110 <u>0111</u>

| 'to' bits to copy to

0111 1000 -----| instr.addr.and rot.amount

1000 0000

instruction 2

1001 0000

1010 0000

1011 1000

1100 0000

1101 0000

1110 0000

1111 0000

```

Instruction\_1 of the following program rotates the bits (0010) of latch 0001 one space to the left (for 0100) and copies all four rotated bits to latch 0010. Notice that, because latch 0110 of instruction\_1 holds 1111, all four bits are copied to. Also notice that, because latch 0111 has 01 in the rightmost two bits, the from data is rotated one bit to the left.

#### Before Rotate 0010 One Bit Left for 0100

| atch | bit                                                                                                  |                                                                                                                                                                             |

|------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ress | values                                                                                               | 3                                                                                                                                                                           |

| 0000 | 0100                                                                                                 | address of instruction                                                                                                                                                      |

| 0001 | 0010                                                                                                 | from data                                                                                                                                                                   |

| 0010 | 0000                                                                                                 | to data                                                                                                                                                                     |

| 0011 | 0000                                                                                                 |                                                                                                                                                                             |

| 0100 | 0001                                                                                                 | from address                                                                                                                                                                |

| 0101 | 0010                                                                                                 | to address                                                                                                                                                                  |

| 0110 | <u>1111</u>                                                                                          | 'to' bits to copy to                                                                                                                                                        |

| 0111 | 10 <u>01</u>                                                                                         | instr.addr.and rot.amount                                                                                                                                                   |

| 1000 | 0000                                                                                                 |                                                                                                                                                                             |

| 1001 | 0000                                                                                                 |                                                                                                                                                                             |

| 1010 | 0000                                                                                                 |                                                                                                                                                                             |

| 1011 | 1000                                                                                                 |                                                                                                                                                                             |

| 1100 | 0000                                                                                                 |                                                                                                                                                                             |

| 1101 | 0000                                                                                                 |                                                                                                                                                                             |

| 1110 | 0000                                                                                                 |                                                                                                                                                                             |

| 1111 | 0000                                                                                                 |                                                                                                                                                                             |

|      | ress<br>0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>1001<br>1011<br>1100<br>1101<br>1110 | ress values 0000 0100 0001 0000 0010 0000 0011 0000 0011 0010 0110 1111 0111 1001 1000 0000 1010 0000 1011 0000 1011 0000 1101 0000 1101 0000 1101 0000 1101 0000 1110 0000 |

After instruction\_1 is executed, the memory has the following values. Latch 0000 now holds  $\underline{10}01$ . The right two bits in latch 0000 do *not* affect what instruction is executed next. The left two bits of  $\underline{10}01$  (in latch 0000) are  $\underline{10}$ , so the next instruction to be executed will be instruction\_2, in latches  $\underline{10}00$ ,  $\underline{10}01$ ,  $\underline{10}10$ , and  $\underline{10}11$ .

#### After Rotate 0010 One Bit Left for 0100

```

latch bit

address values

0000 1001 <----| address of instruction

0001

0010 ---

from data

0010

0100 <--|

to data

0011

0000

instruction_1

0100

0001

| from address

0101

0010

to address

i 'to' bits to copy to

0110

1111

0111

1001 ----- instr.addr.and rot.amount

instruction 2

1000

0000

1001

0000

1010 0000

1011 1000

1100 0000

1101 0000

1110 0000

1111 0000

```

Instruction\_1 of the following program rotates the bits (0010) of latch 0001 two spaces to the left (for 1000) and copies all four rotated bits to latch 0010. Notice that, because latch 0110 of instruction\_1 holds 1111, all four bits are copied to. Also notice that, because latch 0111 has 10 in the rightmost two bits, the from data is rotated two bits to the left.

#### Before Rotate 0010 Two Bits Left for 1000

```

latch bit

address values

0000 0100 address of instruction

0001 <u>0010</u> from data

0010 <u>0000</u>

to data

0011 0000

0100 0001 from address

instruction_1

0101 0010 to address

0110 1111

'to' bits to copy to

0111 10<u>10</u>

instr.addr.and rot.amount

instruction 2

1000 0000

1001

0000

1010 0000

1000

1011

1100 0000

1101 0000

1110 0000

1111 0000

```

After instruction\_1 is executed, the memory has the following values. Again, the right two bits in latch 0000 do *not* affect what instruction is executed next. The left two bits of 1010 (in latch 0000) are 10, so the next instruction to be executed will be instruction\_2, in latches 1000, 1001, 1010, and 1011

#### After Rotate 0010 Two Bits Left for 1000

```

latch bit

address values

0000 1010 <----| address of instruction

0001 0010 ---

from data

0010

1000 <--|

to data

0011

0000

instruction_1

0100 0001

| from address

0101

0010

to address

<u>1111</u>

i 'to' bits to copy to

0110

1010 -----| instr.addr.and rot.amount

0111

instruction 2

1000

0000

1001

0000

1010 0000

1011 1000

1100 0000

1101 0000

1110 0000

1111 0000

```

Instruction\_1 of the following program rotates the bits (0010) of latch 0001 three spaces to the left (for 0001) and copies all four rotated bits to latch 0010. Notice that, because latch 0110 of instruction\_1 holds 1111, all four bits are copied to. Also notice that, because latch 0111 has 11 in the rightmost two bits, the from data is rotated three bits to the left. Notice also that rotating three bits to the left is the same as rotating one bit to the right.

#### **Before Rotate 0010 Three Bits Left for 0001**

```

latch bit

address values

0000 0100 address of instruction

0001 0010 from data

0010 <u>0000</u> to data

0011 0000

0100 0001

from address

instruction 1

0101 0010

to address

0110

<u>1111</u>

'to' bits to copy to

instr.addr.and rot.amount

0111

10<u>11</u>

0000

instruction 2

1000

1001

0000

1010

0000

1011 1000

1100 0000

1101 0000

1110 0000

1111 0000

```

After instruction\_1 is executed, the memory has the following values.

#### After Rotate 0010 Three Bits Left for 0001

```

latch bit

address values

0000 1011 <----| address of instruction

0001 0010 ---|

from data

0010 <u>0001</u> <--

| to data

0011 0000

0100 0001

from address

instruction_1

0101 0010

| to address

0110 <u>1111</u>

| 'to' bits to copy to

0111 10<u>11</u> -----| instr.addr.and <u>rot.amount</u>

1000 0000

instruction 2

1001 0000

1010 0000

1011 1000

1100 0000

1101 0000

1110 0000

1111 0000

```

The right two bits of the last word (four bits here) of an instruction indicate how many bits to rotate to the left according to the following table:

| bit<br>values | rotate<br>left<br>amount |

|---------------|--------------------------|

| 00            | 0                        |

| 01            | 1                        |

| 10            | 2                        |

| 11            | 3                        |

If the rightmost bit value is 1, then there is 1 bit of rotation left. If the left bit value is 1, then there is an additional two bits of rotation left.

The following table shows how rotation works with the four bits of a word labeled 'A,' 'B,' 'C,' and 'D.'

| rotate |      | rotate | rotate |

|--------|------|--------|--------|

| bit    | four | left   | right  |

| values | bits | amount | amount |

| 00     | ABCD | 0      | 0      |

| 01     | BCDA | 1      | 3      |

| 10     | CDAB | 2      | 2      |

| 11     | DABC | 3      | 1      |

Notice again that rotating 3 bits left is the same as rotating 1 bit right. Similarly, 1 bit left is 3 bits right and 2 bits left is 2 bits right.

# **PROCESSOR**

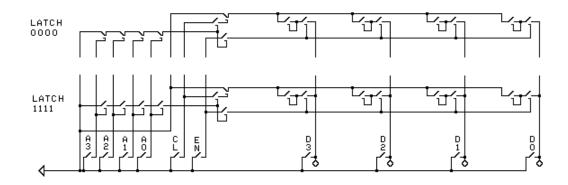

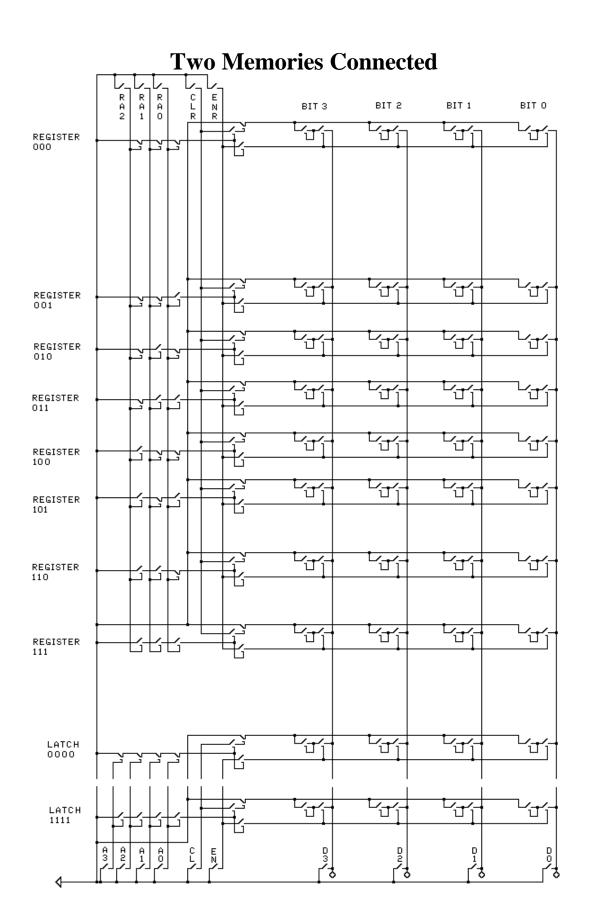

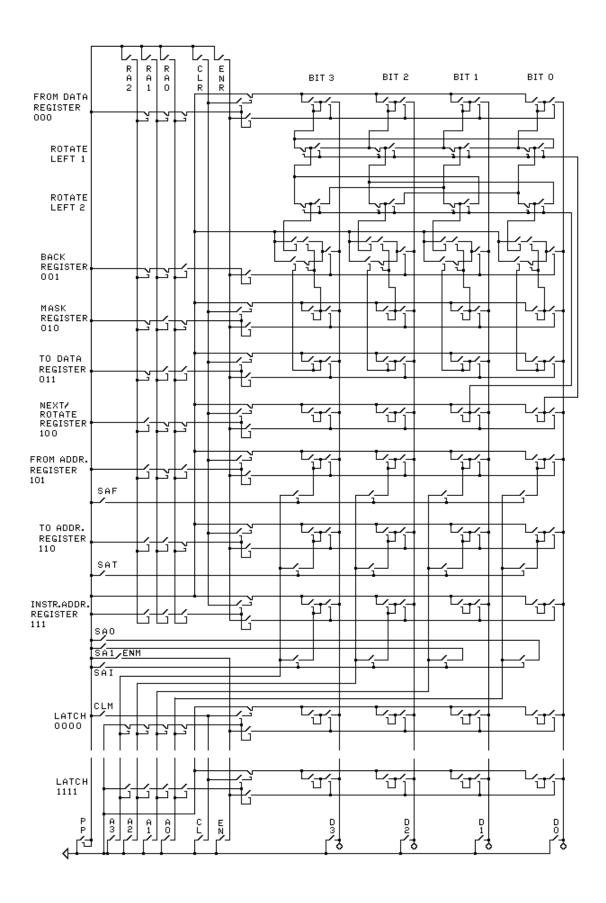

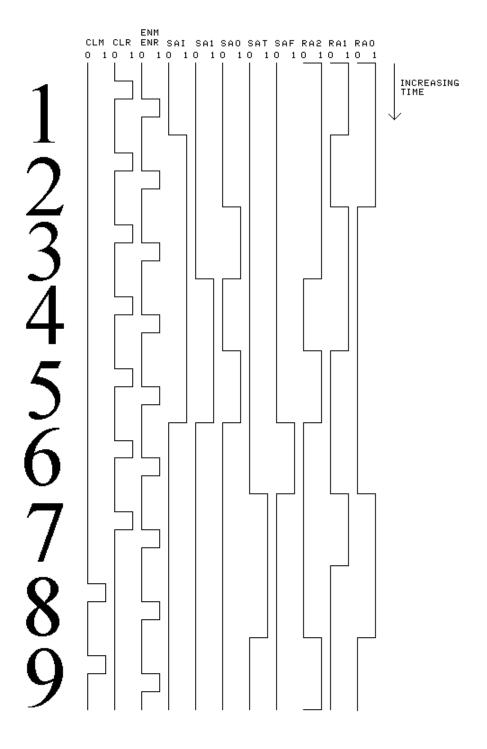

### **Four-Bit Memory**

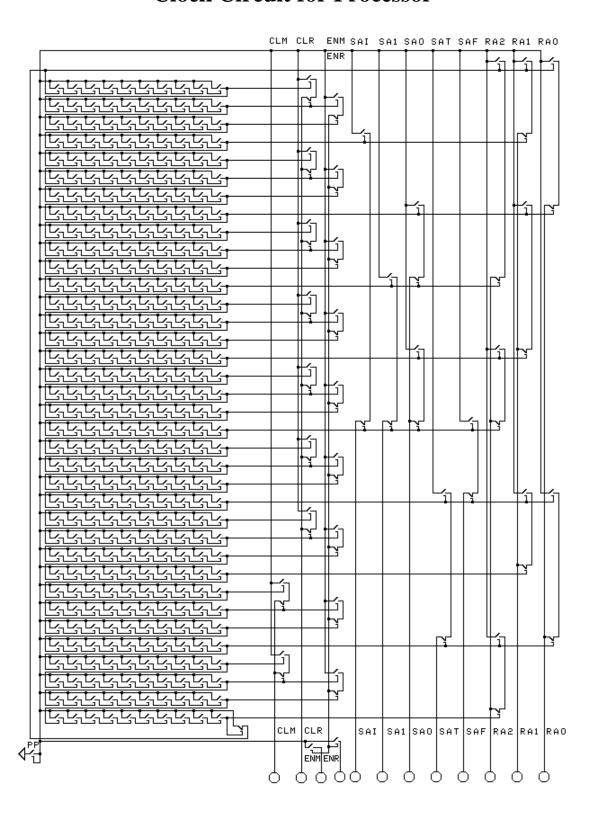

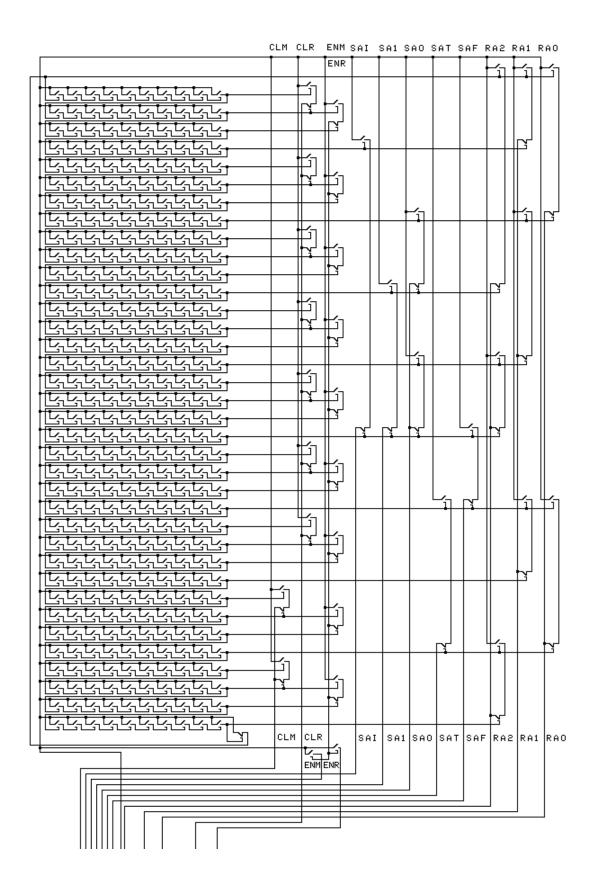

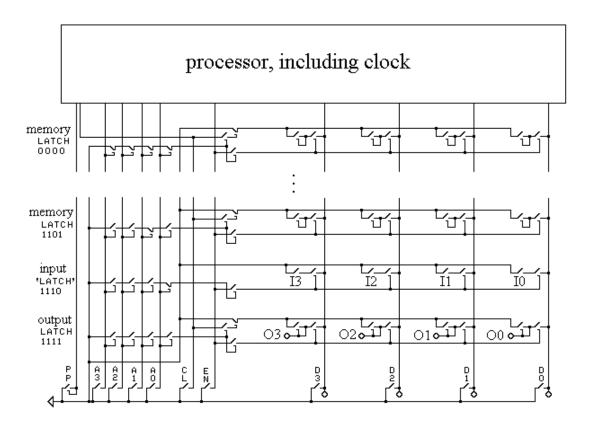

The circuit above shows a memory with four data wires (D3, D2, D1, and D0) and four address wires (A3, A2, A1, and A0). Because there are four address wires, there are sixteen possible latch addresses: 0000, 0001, 0010, 0011, 0100, 0101, 0110, 0111, 1000, 1001, 1010, 1011, 1100, 1101, 1110, and 1111. Only two latches, 0000 and 1111, are shown. The rest are implied by the gap in the circuit diagram.

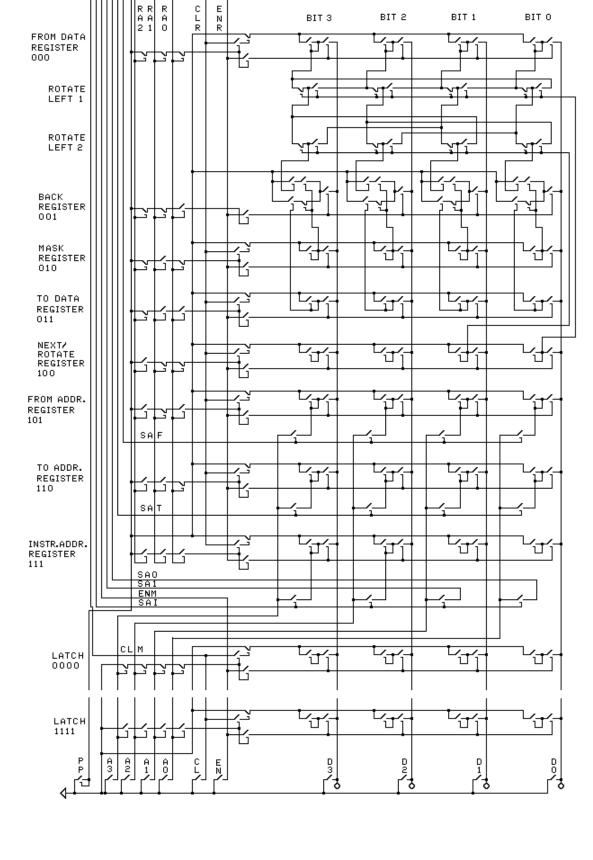

The circuit diagram above shows a memory with four address wires on the bottom connected with a memory with three address wires on the top. Room has been left in the top memory for additional circuitry later. The two memories share data wires D3, D2, D1, and D0. The three-address-wire memory has address wires RA2, RA1, and RA0, clear wire CLR, and enable wire ENR. In the top memory, the latches are called registers and the address wires are called RA2 for Register Address 2, etc. CLR stands for CLear Register. ENR stands for ENable Register.

Because both memories share data wires D3, D2, D1, and D0, data can be copied from a latch of the bottom memory to a register of the top memory or from a register to a latch.

To copy data from a latch to a register, first select the register with register address keys RA2, RA1, and RA0. Second, temporarily press the CLR key to clear the register loops to all 0's. Third, select the latch address with address keys A3, A2, A1, and A0 (while continuing to select the register with RA2, RA1, and RA0). Fourth, temporarily press the enable keys, ENR and EN, to connect the selected register loops and the selected latch loops to the data wires D3, D2, D1, and D0.

Similarly, to copy data from a register to a latch, first select the latch with address keys A3, A2, A1, and A0. Second, temporarily press the clear key, CL (*not* CLR), to clear the *latch*. Third, select the register with register address keys RA2, RA1, and RA0. Fourth, temporarily press the enable keys, ENR and EN. This connects the register and latch loops to the data bus wires, D3, D2, D1, and D0, and, thereby, to each other.

## **Loops Controlling Lights**

The circuit above shows four loops controlling four lights.

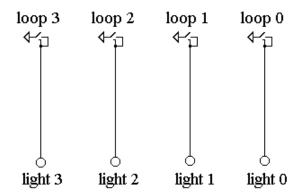

### **Rotate 1 Circuitry**

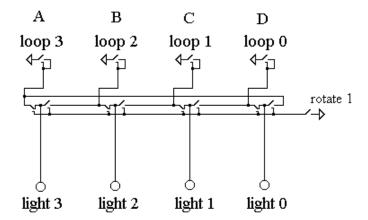

In the circuit above, if the 'rotate 1' key is *not* pressed, then loop3 controls light 3, loop 2 controls light 2, loop 1 controls light 1, and loop 0 controls light 0.

However, if the 'rotate 1' key *is* pressed, then loop 3 controls light 0, loop 2 controls light 3, loop 1 controls light 2, and loop 0 controls light 1. One can say that when the 'rotate 1' key is pressed, then the loop values are rotated one bit to the left. There is *no* bit to the left of bit 3, so bit 3 is rotated to the right end to bit 0.

The following table indicates what pressing the 'rotate 1' key does.

| Rotate 1 | Light Values |   |   |   | Rotate left    |

|----------|--------------|---|---|---|----------------|

|          | 3            | 2 | 1 | 0 | amount in bits |

|          |              |   |   |   |                |

| 0        | A            | В | С | D | 0              |

### **Rotate Two Bits Circuitry**

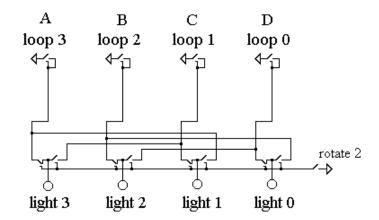

In the circuit above, if the 'rotate 2' key is *not* pressed, then loop 3 controls light 3, loop 2 controls light 2, loop 1 controls light 1, and loop 0 controls light 0.

However, if the 'rotate 2' key *is* pressed, then loop 3 controls light 1, loop 2 controls light 0, loop 1 controls light 3, and loop 0 controls light 2. One can say that when the 'rotate 2' key is pressed, then the loop values are rotated two bits to the left.

The following table indicates what pressing the 'rotate 2' key does.

| Rotate 2 | Light Values |   |   |   | Rotate left    |

|----------|--------------|---|---|---|----------------|

|          | 3            | 2 | 1 | 0 | amount in bits |

| 0        | A            | В | С | D | 0              |

| 1        | С            | D | A | В | 2              |

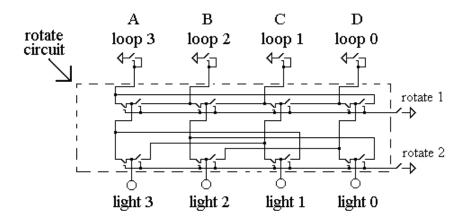

### **Rotate Circuitry**

In the circuit above, if *neither* the 'rotate 1' key nor the 'rotate 2' key is pressed, then loop 3 controls light 3, loop 2 controls light 2, loop 1 controls light 1, and loop 0 controls light 0. If rotate 1 is pressed and rotate 2 is *not* pressed, then the loop signals are rotated 1 bit to the left on the way to the lights. If rotate 2 is pressed and rotate 1 is *not* pressed, then the loop values are rotated 2 bits to the left on the way to the lights. Finally, if *both* the rotate 1 key and the rotate 2 key are pressed, then the loop values are rotated three bits to the left. For example, the value in loop 0 is routed to light 3.

The following table indicates what pressing one or both 'rotate' keys does.

| Rotate 2 | Rotate 1 | Light values |   |   |   | Rotate left    |

|----------|----------|--------------|---|---|---|----------------|

|          |          | 3            | 2 | 1 | 0 | amount in bits |

| 0        | 0        | A            | В | С | D | 0              |

| 0        | 1        | В            | С | D | Α | 1              |

| 1        | 0        | С            | D | A | В | 2              |

| 1        | 1        | D            | A | В | C | 3              |

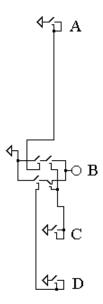

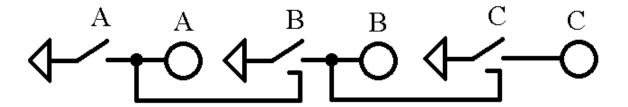

## **Mask Circuitry**

In the circuit above, if loop C has value 0, then light B gets the value in loop D. If loop C has value 1, then light B gets the value in loop A.

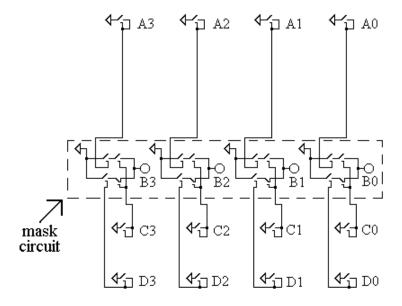

## **Mask Four Bits**

In the left circuit above, C3 controls whether the value of A3 or the value of D3 goes to B3. The other circuits behave similarly.

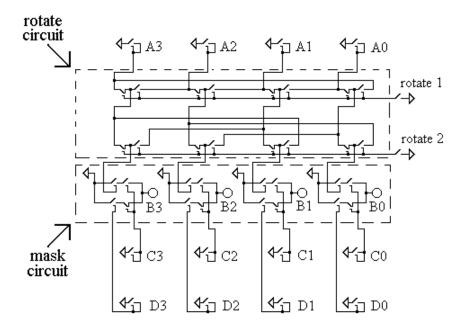

#### **Rotate and Mask**

In the circuit above, there is a 'rotate circuit' and a 'mask circuit.'

As an example of the operation of this circuit, consider the case of 'rotate 1' being pressed, 'rotate 2' *not* pressed, C3 = 1, C2 = 1, C1 = 0, and C0 = 0. Then B3 gets A2, B2 gets A1, B1 gets D1, and B0 gets D0. Try to follow the signals in the circuit and see why.

This will be the logic unit of our simple processor. (The logic units of most processors do arithmetic too and so are called arithmetic logic units or, abbreviating, ALU's.)

## **Delay Circuitry**

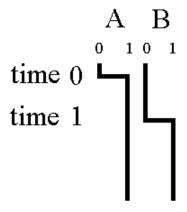

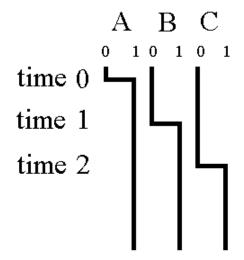

In the circuit above, when key A is pressed, electromagnet B is powered and key B closes. It takes time for B to close after A is pressed. That is, light B comes on about one hundredth of a second after light A. This is indicated by the following 'timing diagram' that shows when the lights come on. Time 0 is 0 seconds. Time 1 is one hundredth of a second (later).

## **Timing Diagram for Lights**

## **Two Delays**

In the circuit above, after key A is pressed it takes one hundredth of a second for key B to close. After key B closes, it takes one hundredth of a second for key C to close. Therefore, after key A is pressed, it takes two hundredths of a second for light C to come on. In the following timing diagram for the circuit above, time 0 is 0 seconds, time 1 is one hundredth of a second, and time 2 is two hundredths of a second.

## **Timing Diagram for Lights**

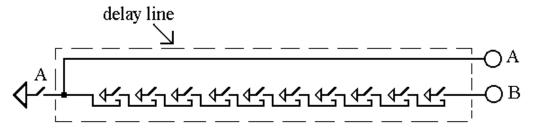

## **Delay Line**

In the circuit (called a delay line) above, light B comes on ten hundredths of a second after light A. Ten hundredths of a second is one tenth of a second, so light B comes on one tenth of a second after key A is pressed (as indicated in the diagram below). (The small amount of time between the time key A is pressed and the time light A comes on is ignored.) Time 0 is 0 seconds and time 1 is one *tenth* of a second in the diagram below.

(When a key closes, it can bounce open and closed a few times. This possible problem will be ignored, except to say that using normally closed relays in a delay line might reduce the problem. This problem does not exist in a delay line made with transistors.)

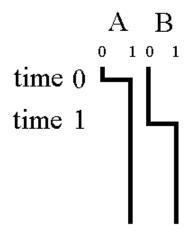

### **Timing Diagram for Delay Line**

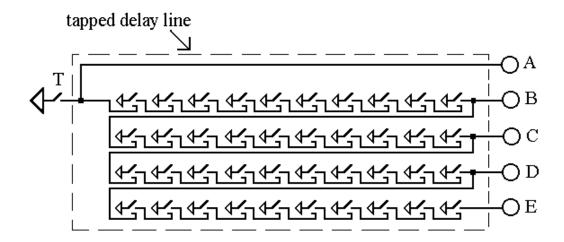

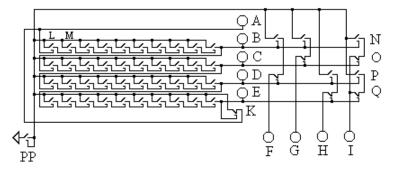

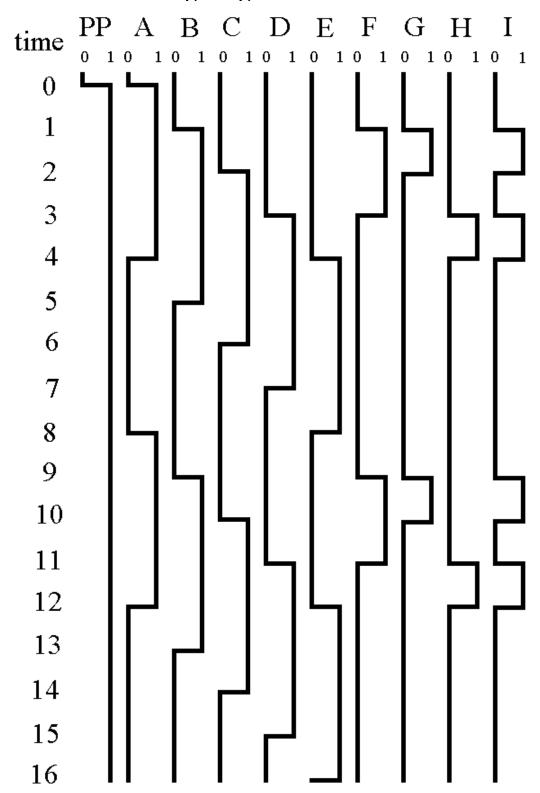

## **Tapped Delay Line**

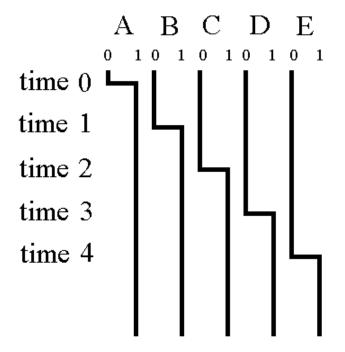

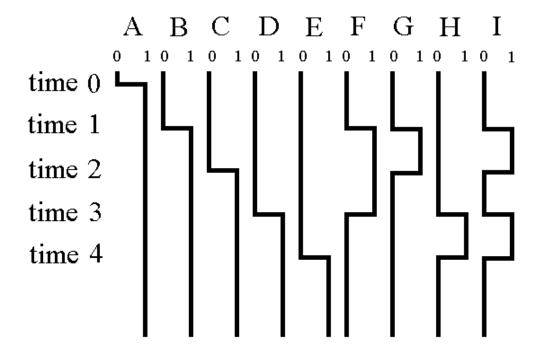

The circuit above is called a tapped delay line. Wires A, B, C, D, and E are called taps. Light B comes on one *tenth* of a second after light A, light C comes on two tenths of a second after light A, light D comes on three tenths of a second after light A, and light E comes on four tenths of a second after light A (as indicated in the timing diagram below).

# **Timing Diagram for Tapped Delay Line**

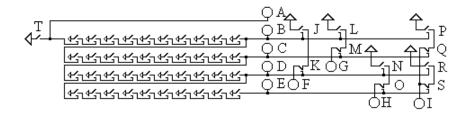

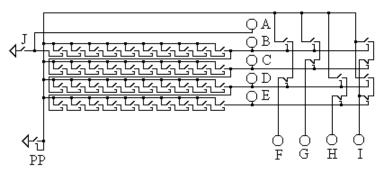

# **Timing Circuit**

# **Timing Circuit's Timing Diagram**

The timing diagram at left corresponds to the circuit above. Lights A, B, C, D, and E come on, in order, as before. However, the behaviors of lights F, G, H, and I are more complex.